数字逻辑设计:自动操作

一、寄存器

用来暂时存放参与运算的数据和运算结果。把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。

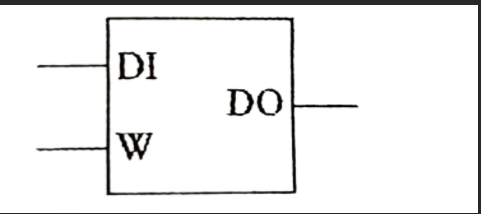

- 注意看,这本来是一个D触发器,由于命名方式的改变,他的D:数据输入端被更名为DI(即Data In),他的时钟信号端被命名为W(写操作端,Write),他原来的输出端Q被命名为DO(Data Out)

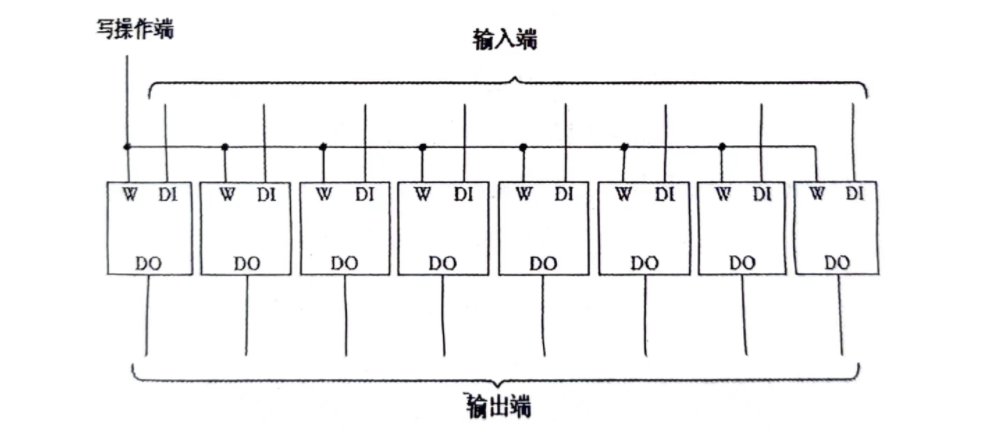

将他们以同步时序电路的方式”并联“:

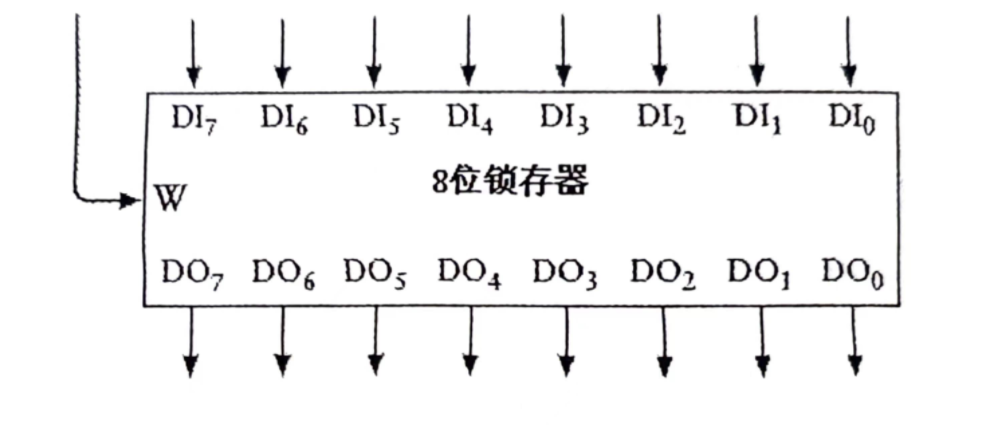

可以得到一个八位寄存器(《code》中用八位锁存器代指这个概念,以下图片不作区分)

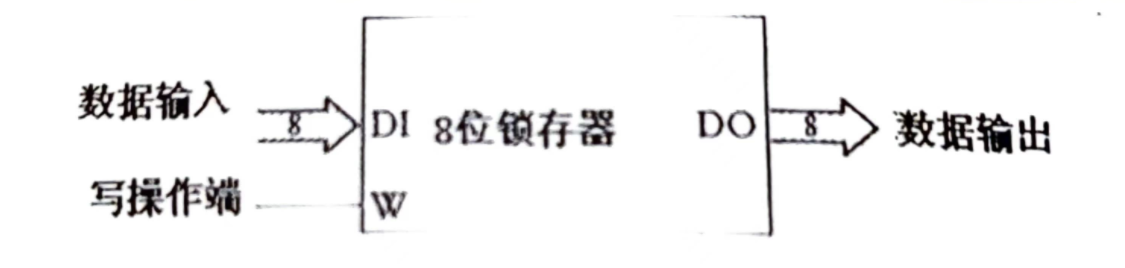

可以简化为如下所示的图:

二、随机存储器(RAM)的基本结构

- 又名“读/写存储器”

读写操作很自由,只需要改变地址及相关的输入,就可以从寄存器中读出或写入需要的数据

-

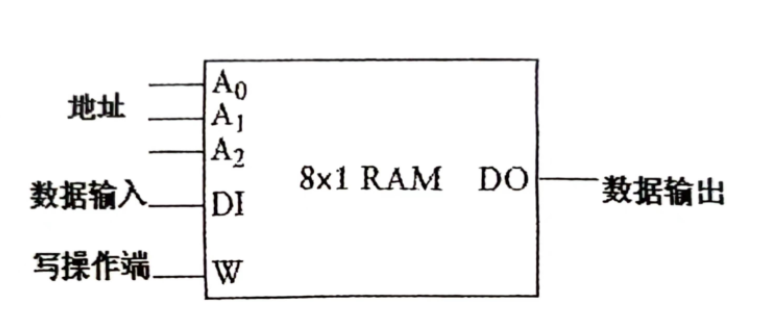

随机访问存储器的符号

-

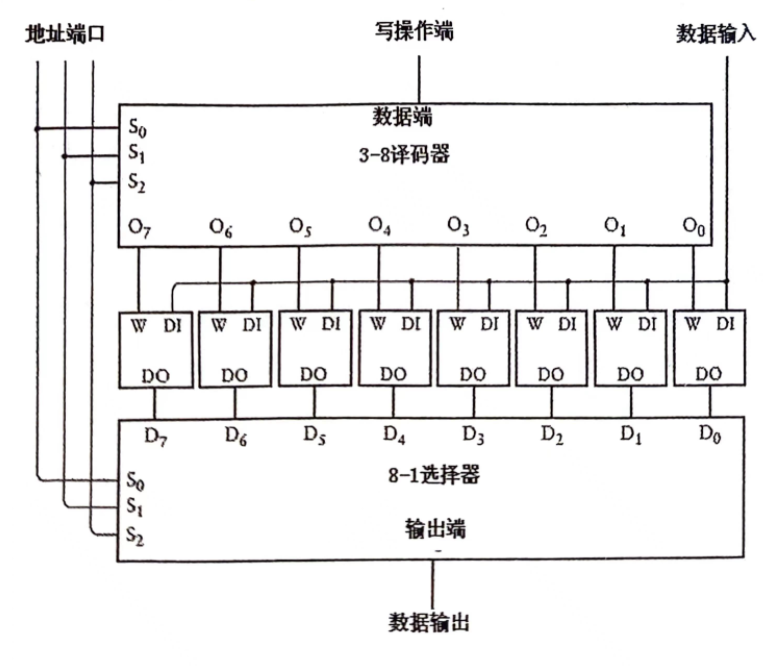

随机存储器的组成:译码器+寄存器+选择器

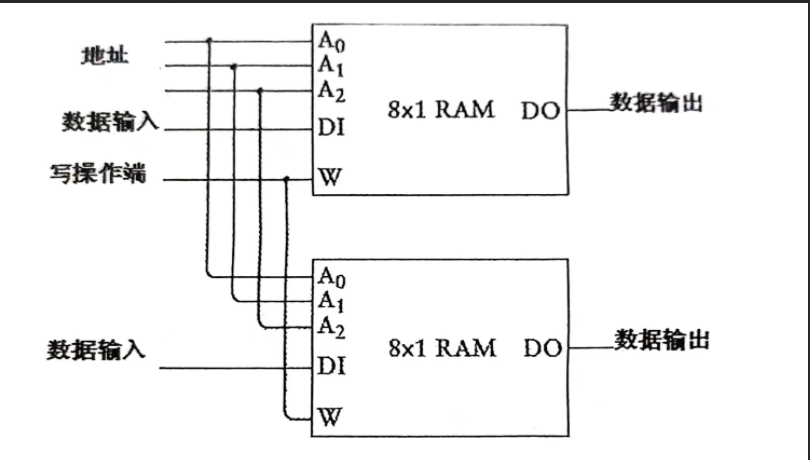

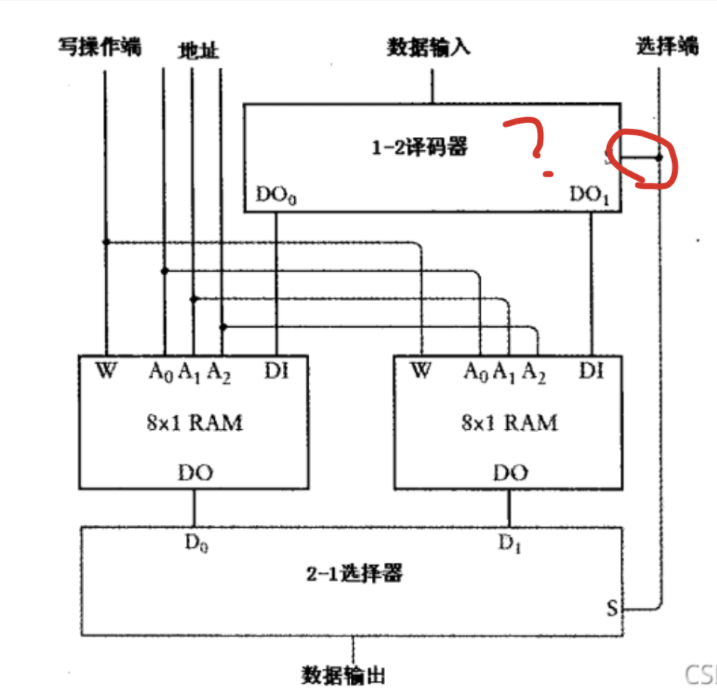

将两个RAM组合成RAM阵列

这个RAM阵列可以存储的二进制数依然是8个,但每个数的位宽为2位。

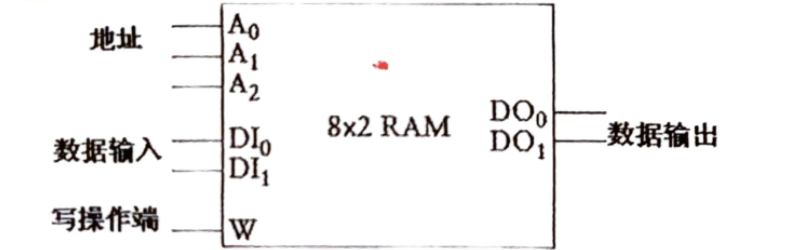

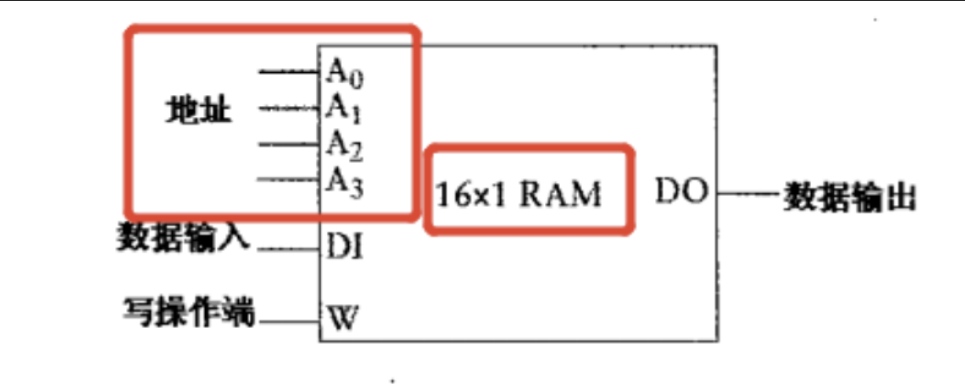

使用2个的RAM搭一个的RAM

-

相当于把两个3-8译码器用一个1-2译码器联结起来

-

下方用一个2-1选择器把两个8-1选择器联结起来

(红圈部分不太理解是什么意思)

S作为选择端,本质上用于选择存储的信息,所以可以并入地址端(A_3端即为S端)

-

注意:中

-