随机存储器(RAM)与只读存储器(ROM)

一、寄存器

用来暂时存放参与运算的数据和运算结果。把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。

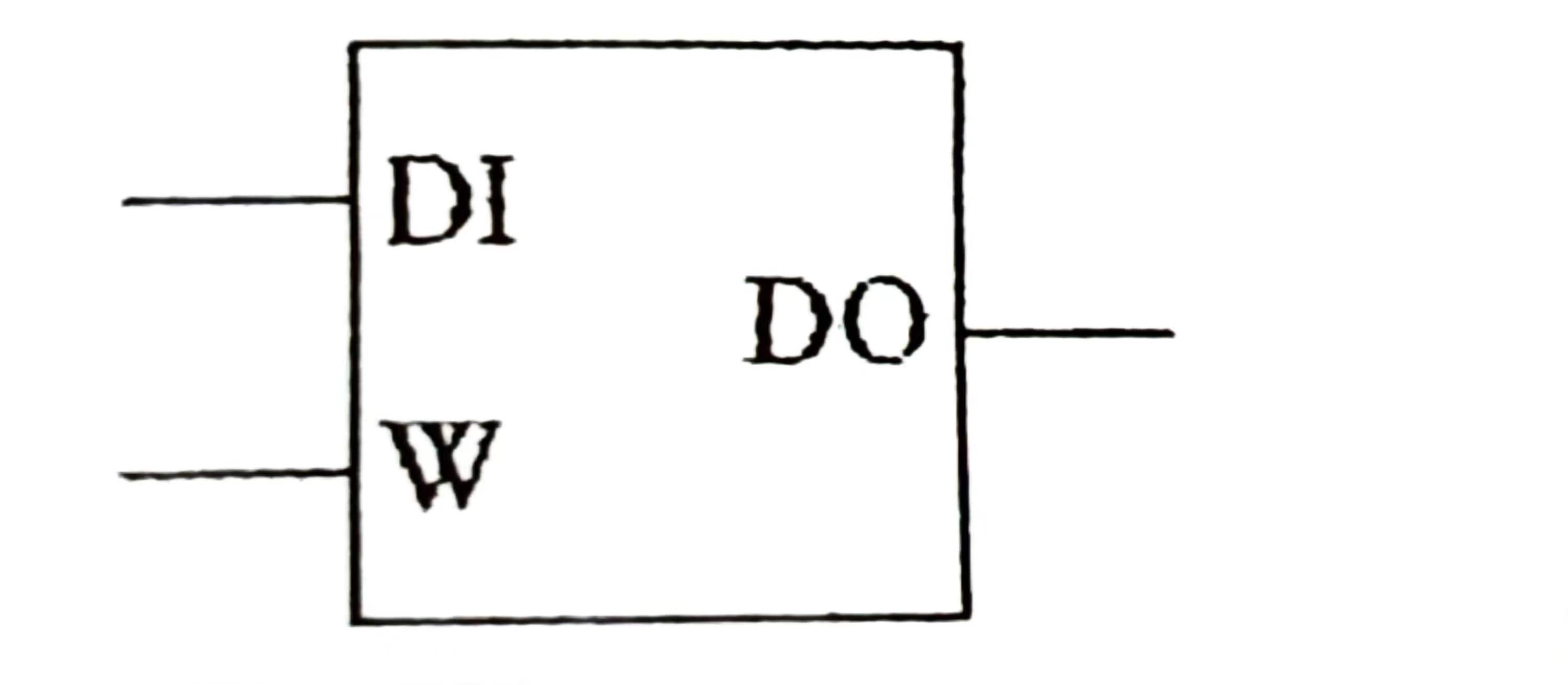

- 注意看,这本来是一个D触发器,由于命名方式的改变,他的:数据输入端被更名为(即Data In),他的时钟信号端被命名为W(写操作端,Write),他原来的输出端Q被命名为DO(Data Out)

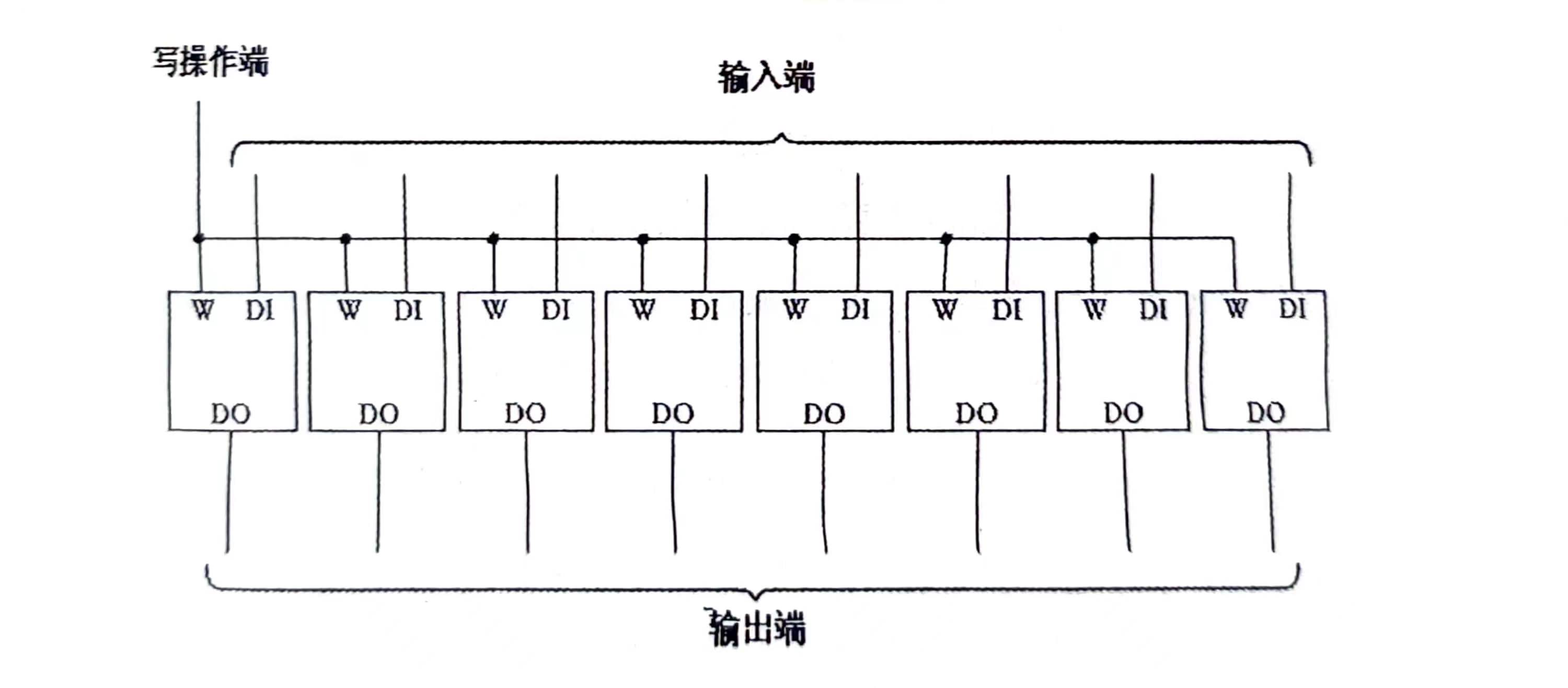

将他们以同步时序电路的方式”并联“:

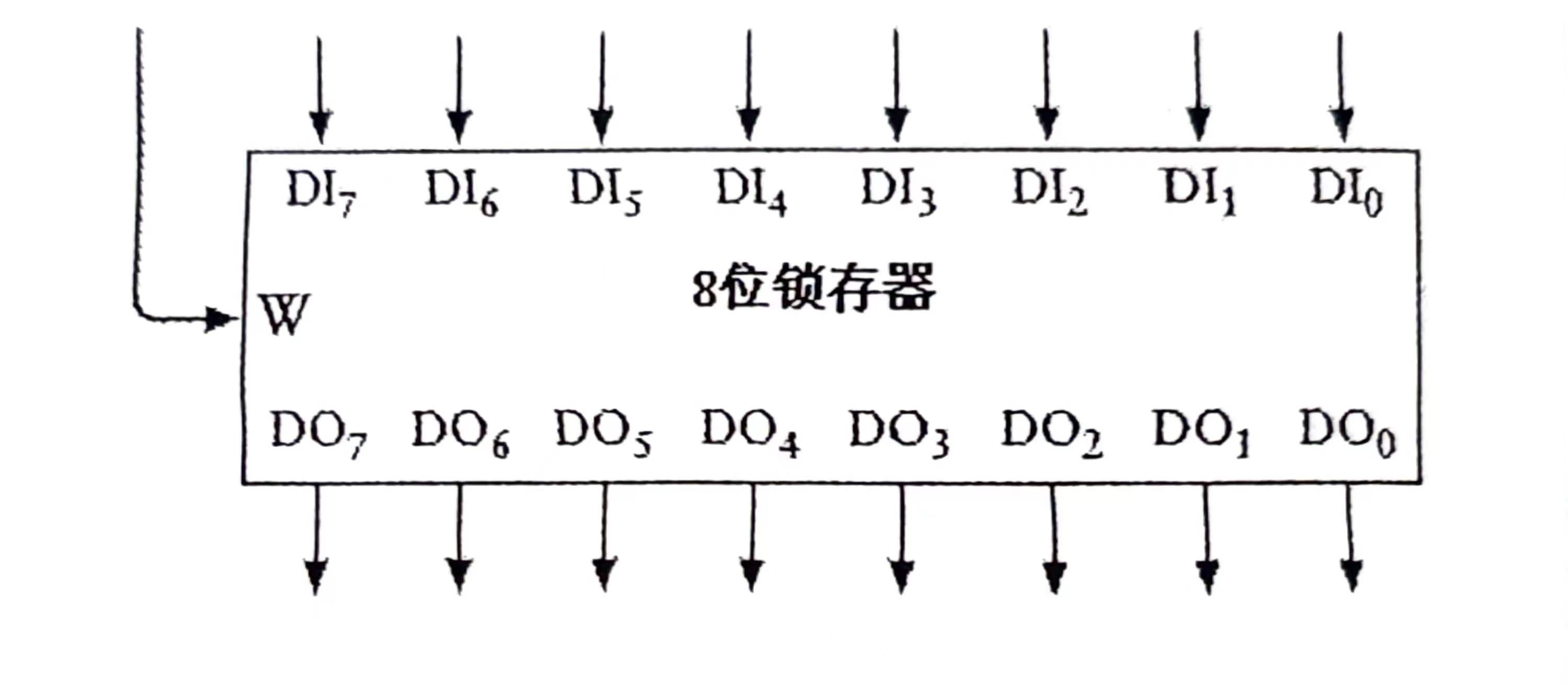

可以得到一个八位寄存器(《code》中用八位锁存器代指这个概念,以下图片不作区分)

可以简化为如下所示的图:

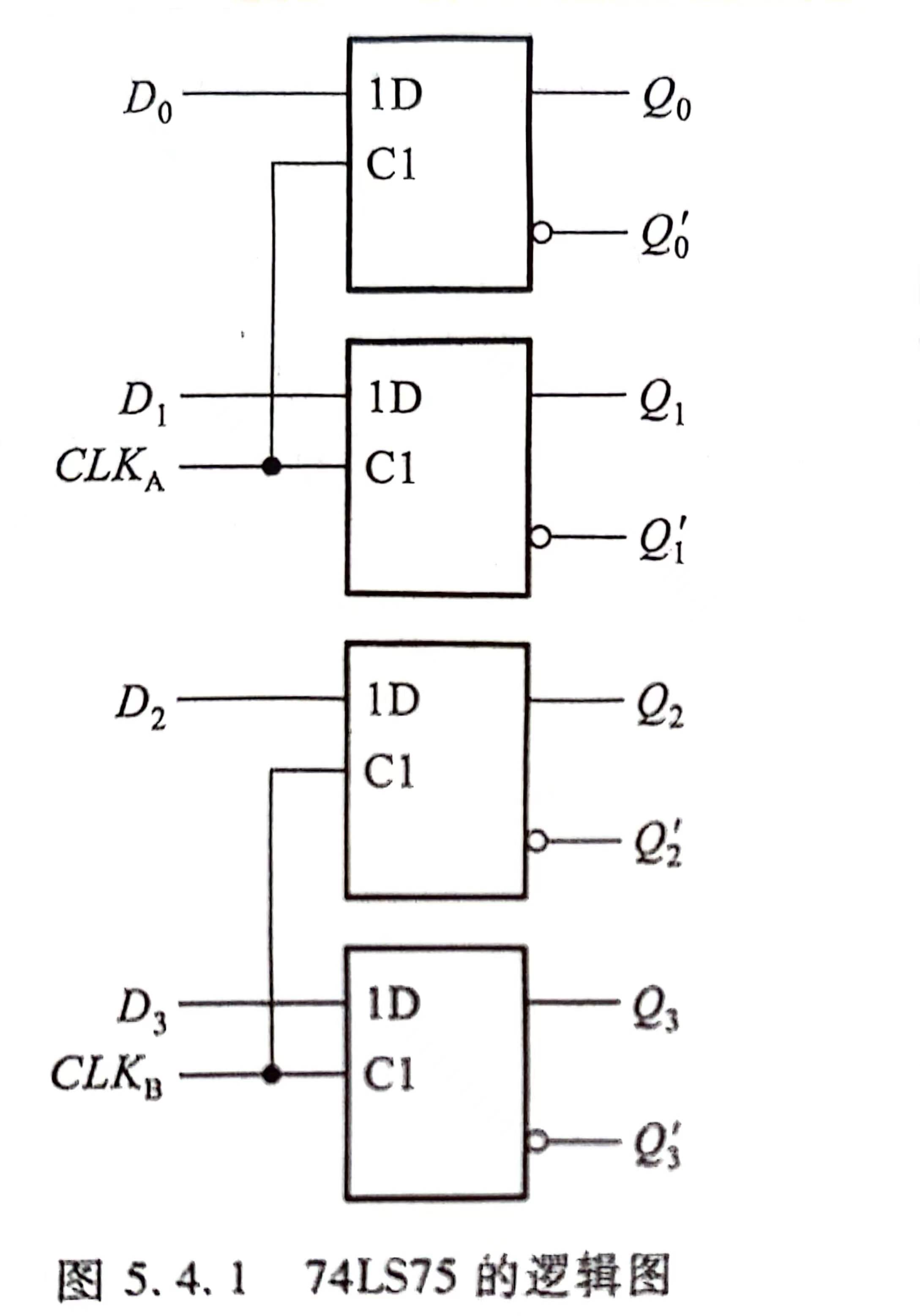

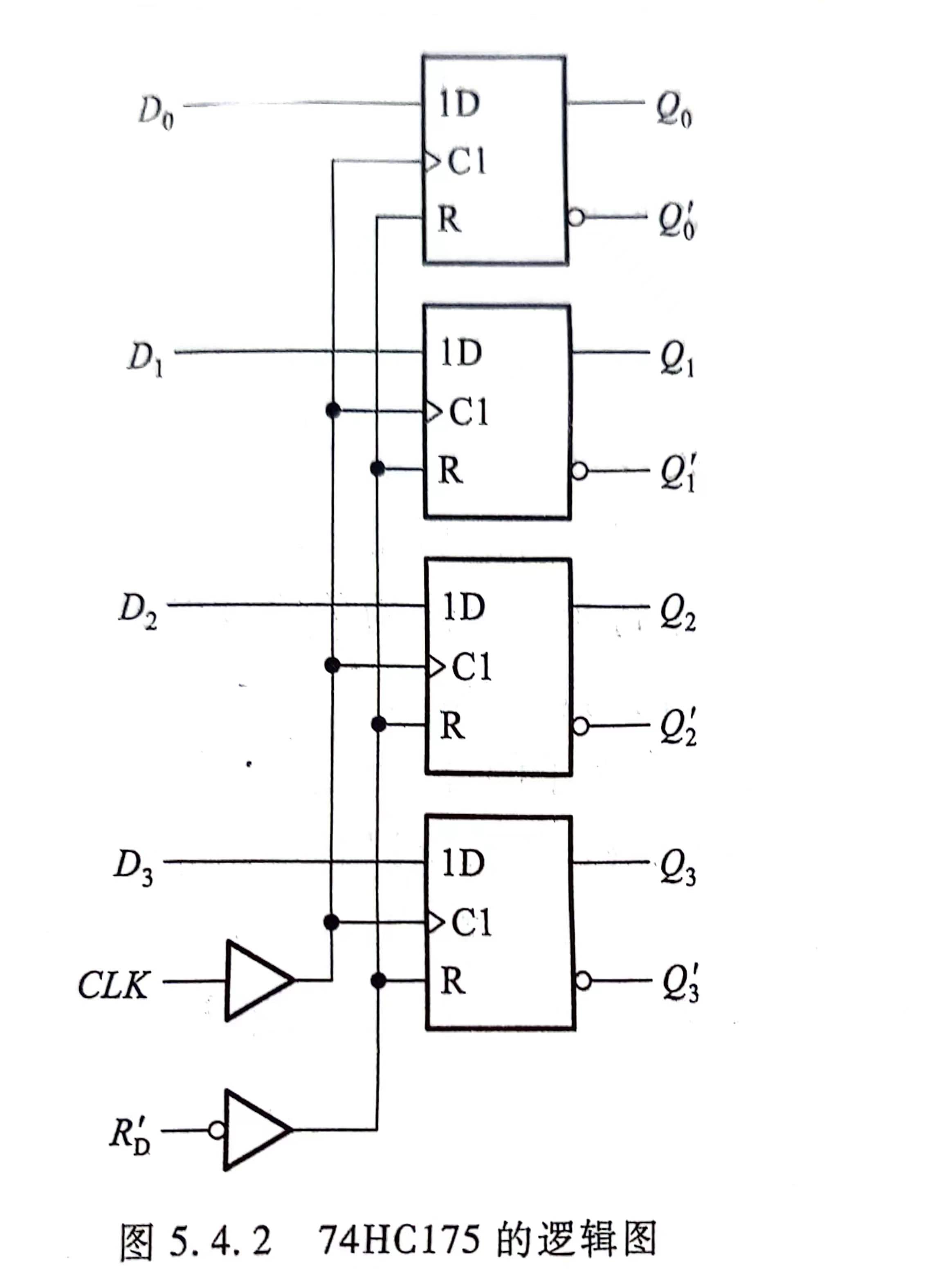

实际应用的寄存器如图所示:包括74LS75和74HC175

二、随机存储器(RAM)的基本结构

- 又名“读/写存储器”

读写操作很自由,只需要改变地址及相关的输入,就可以从寄存器中读出或写入需要的数据

-

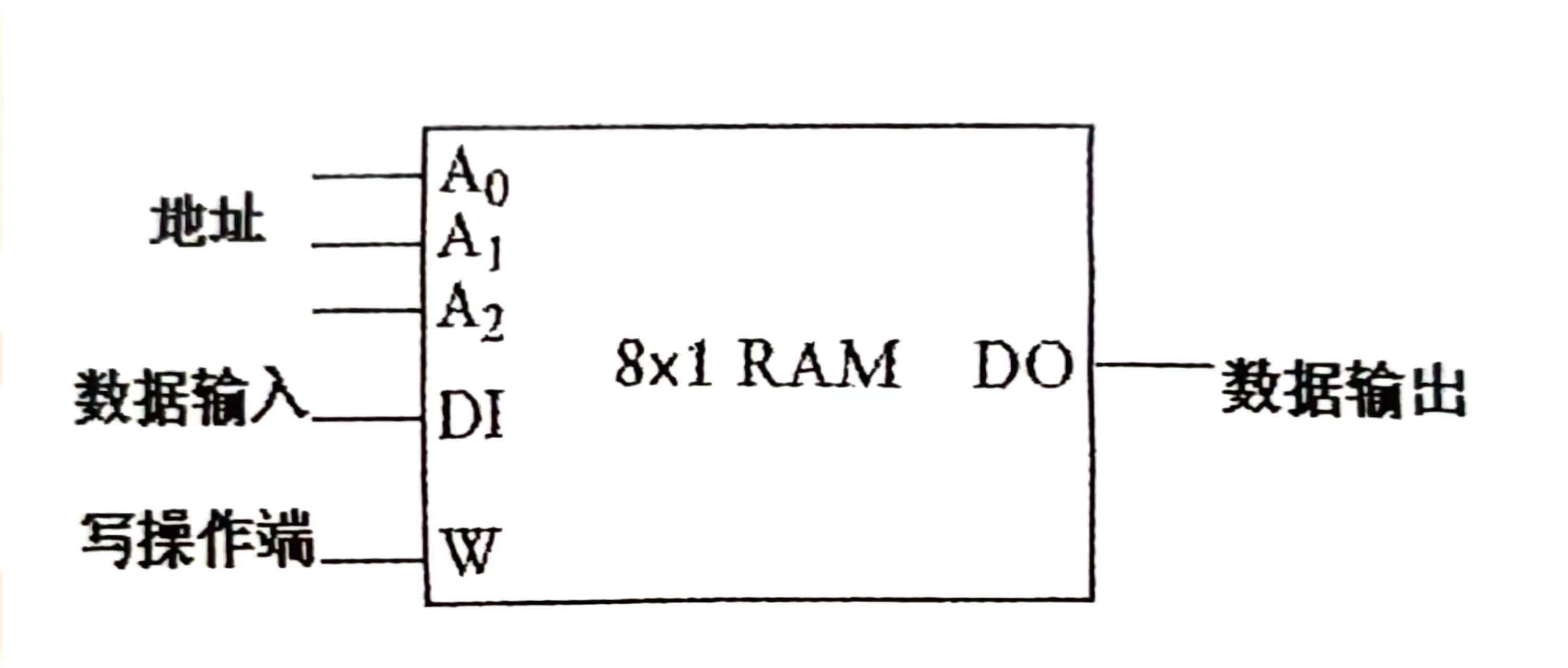

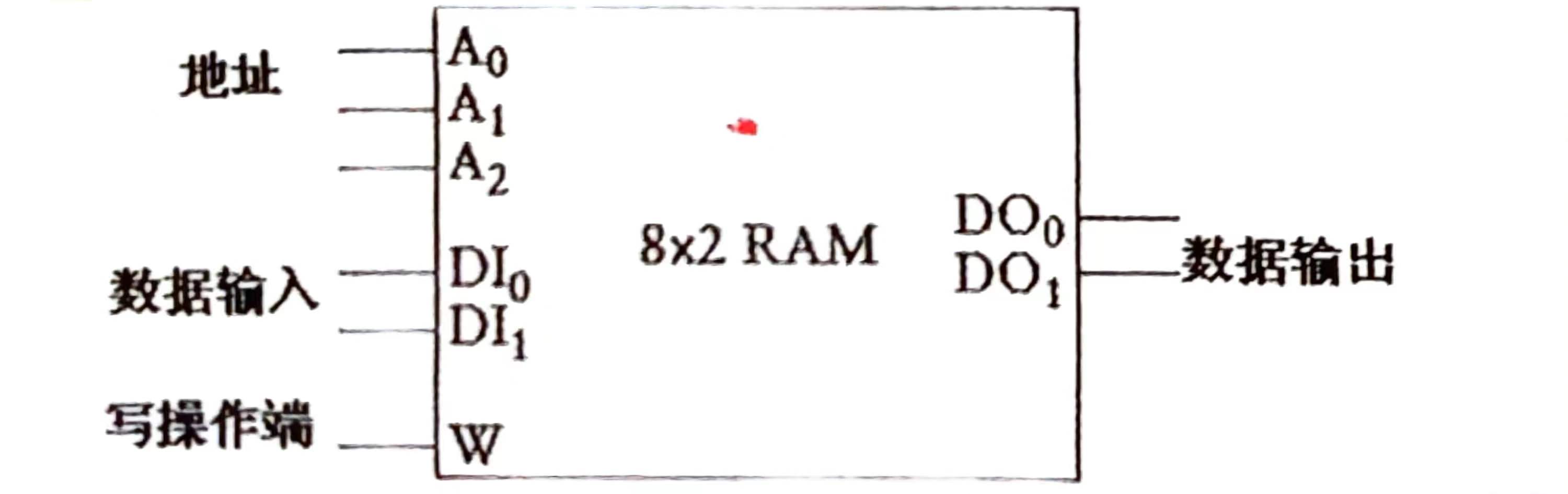

随机访问存储器的符号

-

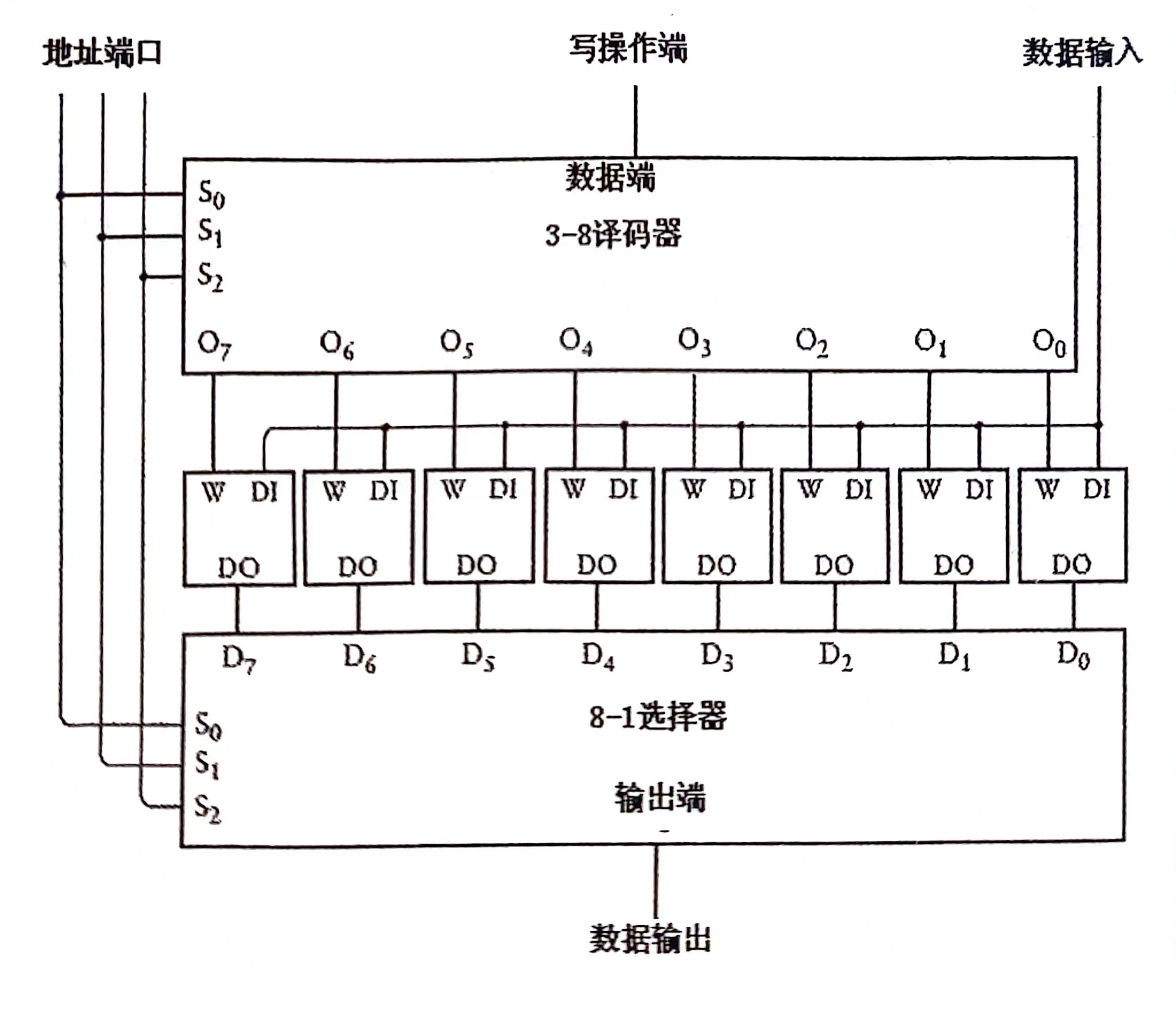

随机存储器的组成:译码器+寄存器+选择器

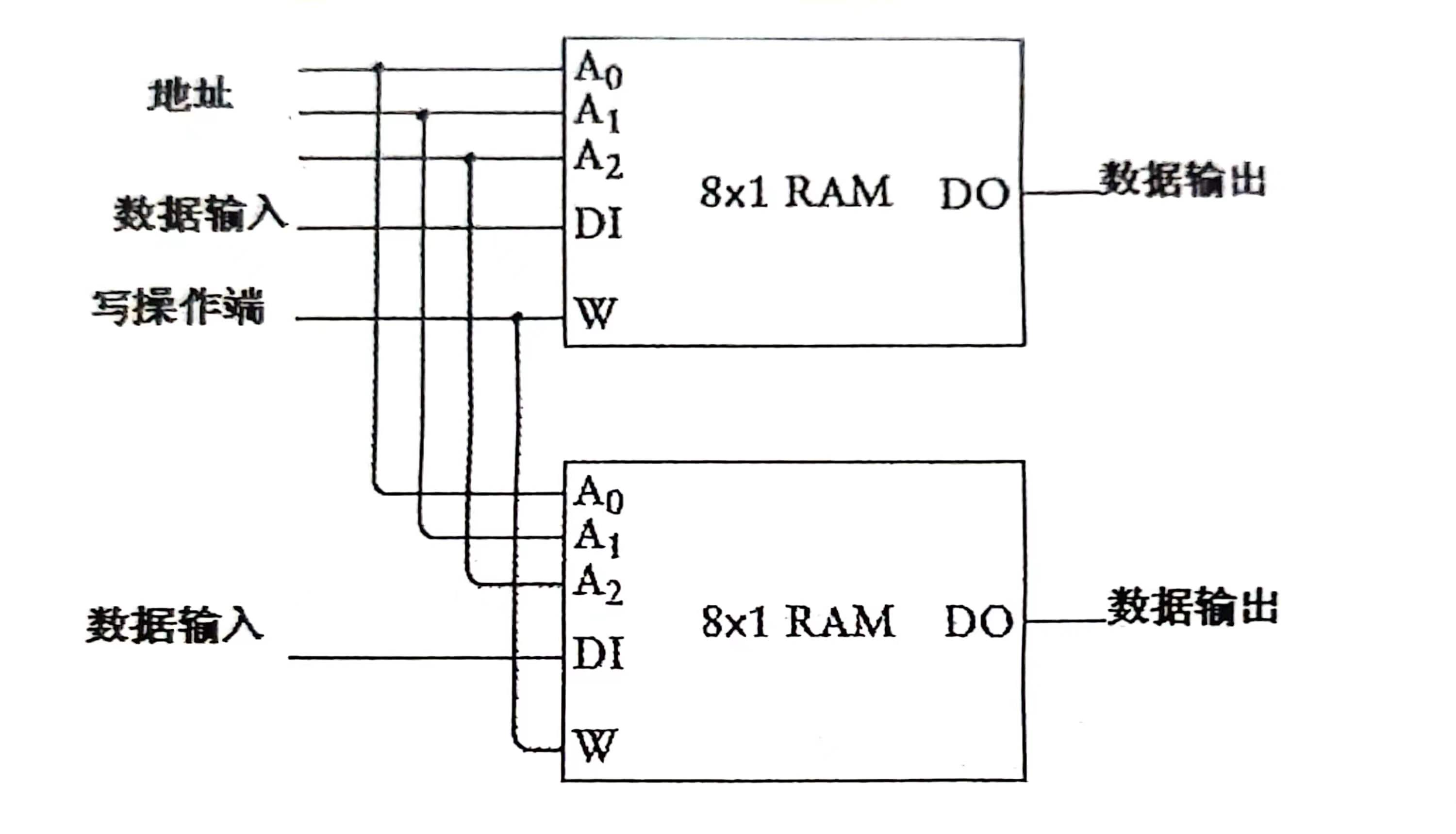

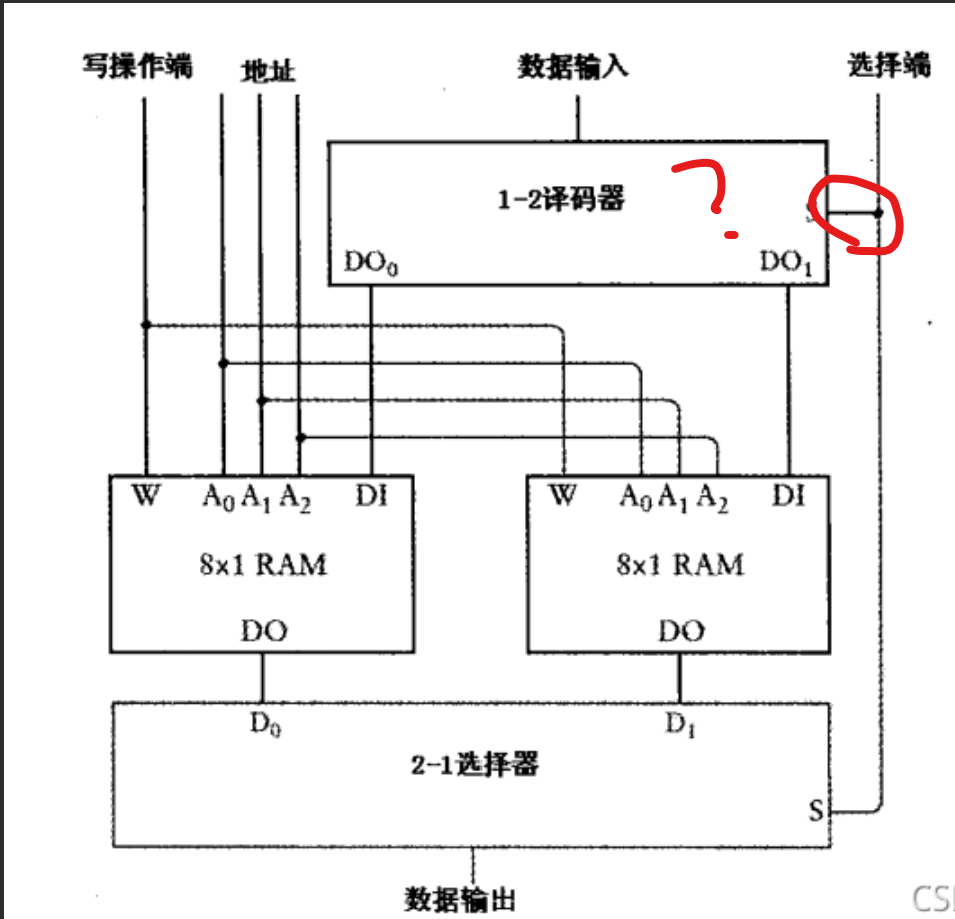

将两个RAM组合成RAM阵列

这个RAM阵列可以存储的二进制数依然是8个,但每个数的位宽为2位。

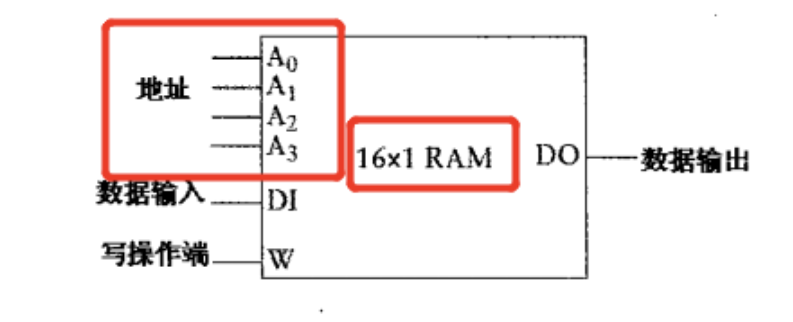

使用2个的RAM搭一个的RAM

-

相当于把两个3-8译码器用一个1-2译码器联结起来

-

下方用一个2-1选择器把两个8-1选择器联结起来

(红圈部分不太理解是什么意思)

S作为选择端,本质上用于选择存储的信息,所以可以并入地址端(端即为端)

-

注意:中

-

前一个数字 = 存储RAM阵列的存储容量 =

-

后一个数字 = 每个单位由几位二进制数构成 = 数据输入端的个数

-

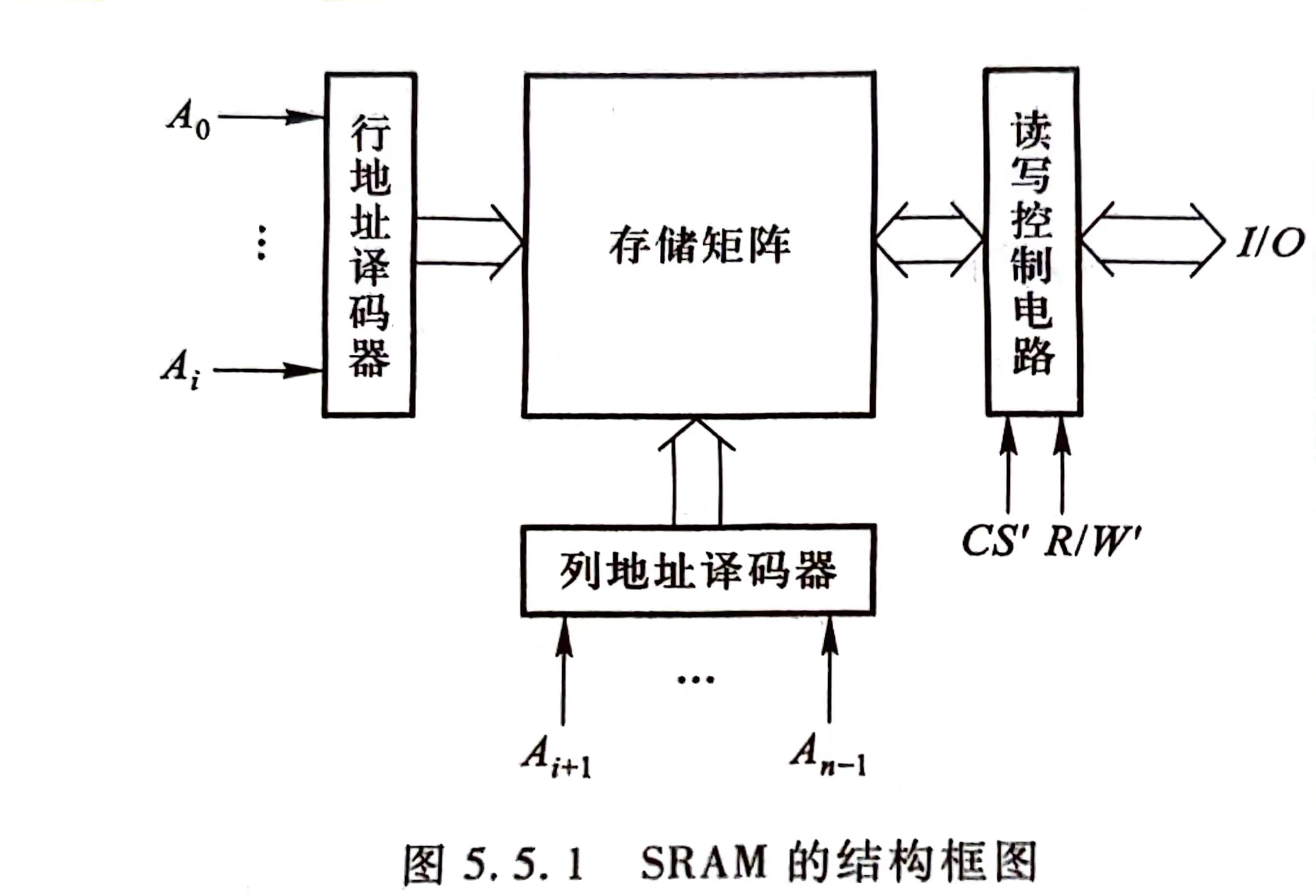

三、静态随机存储器(SRAM)

相比于上面的结构的改进:合并了选择器和译码器的功能,调整为不管是写入还是读出,都由译码器确定需要操作的元素的地址

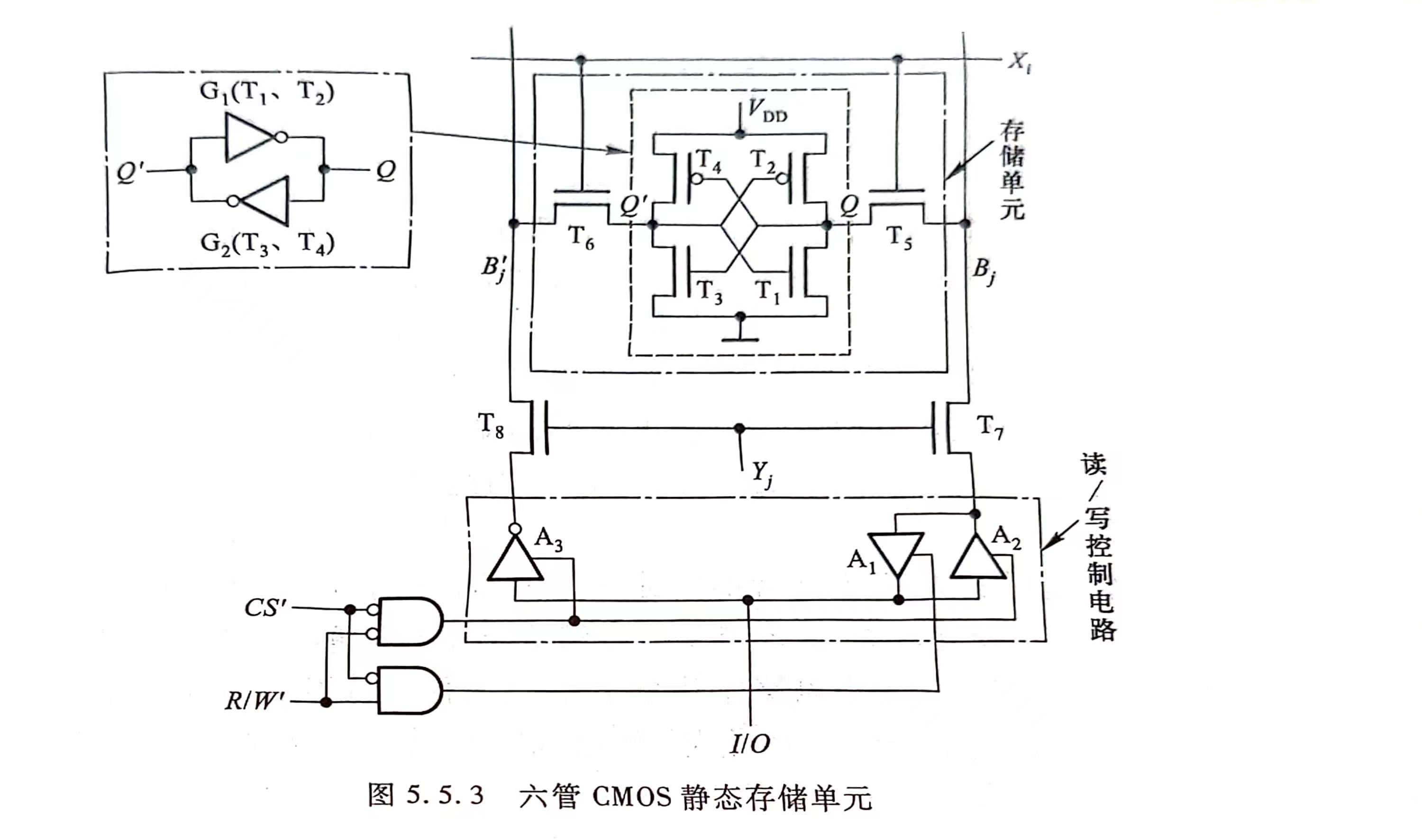

- SRAM的静态存储单元:六管CMOS静态存储单元

看着非常复杂,其实上,它本质就是靠着锁存器自锁功能来存储数据的,

~组成SR锁存器,用于记忆1位二进制代码,其中,和,分别接成了反相器和

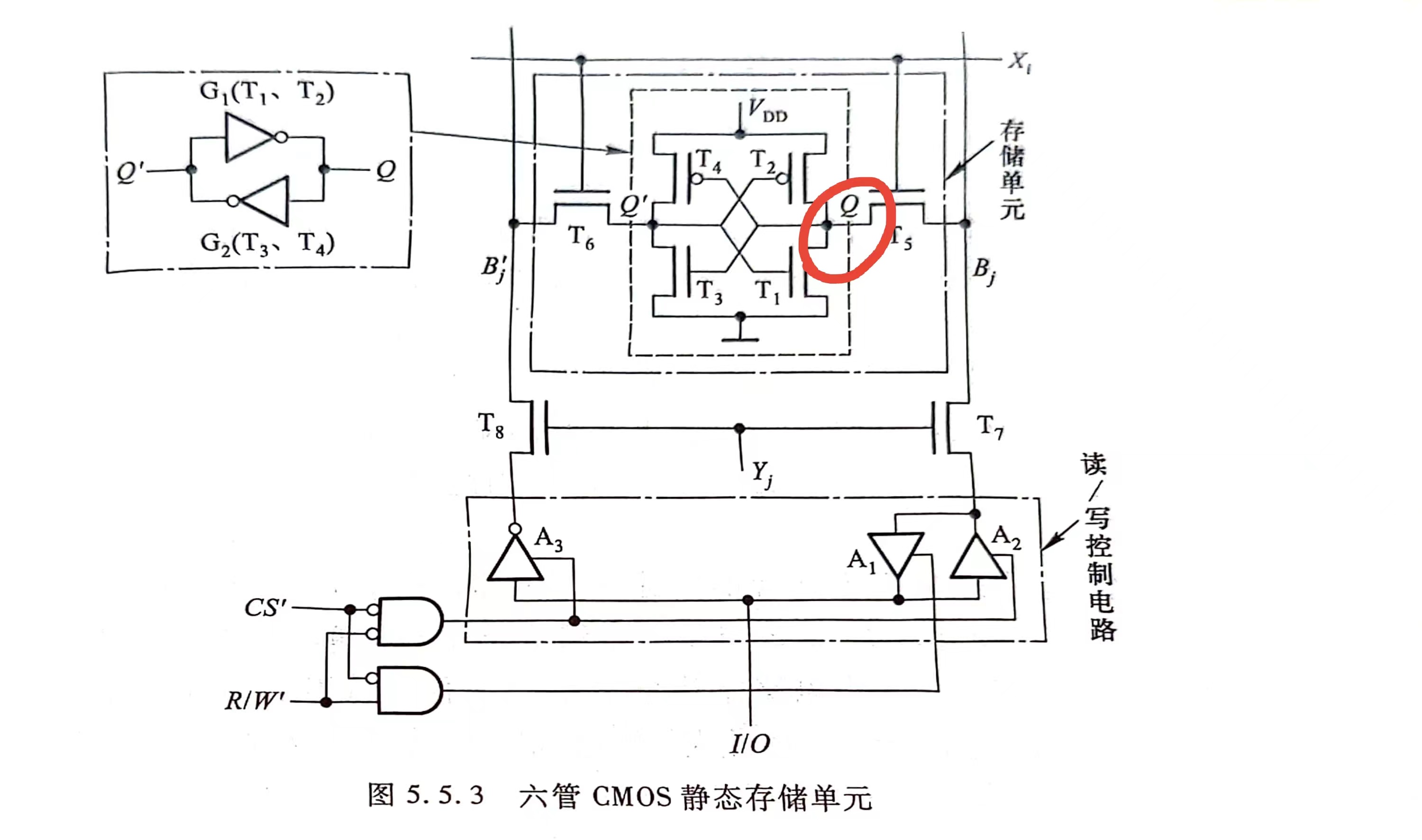

注意看这个Q,他是存储这一位信息的地方(也就是原来的一位锁存器的输出)

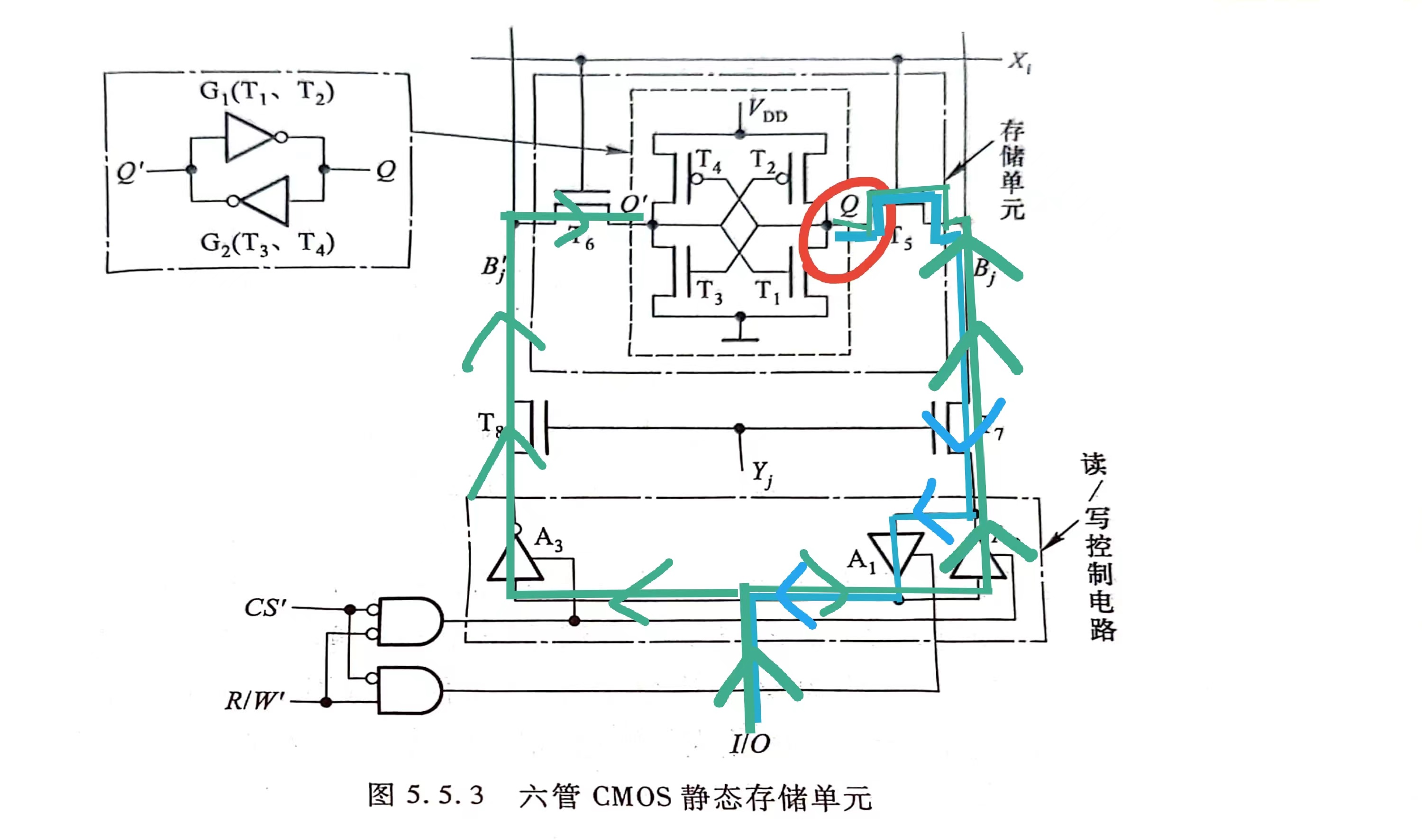

当CS=0时候表示电路可以启动了,此时:

-

当端口输入1时,代表读取模式,数据沿蓝色线从 到 ;

-

当端口输入0时,代表写入模式,数据沿绿色线从 到 ;

当然,实现以上数据传递,需要 和 线都接上高电平。这需要这一位被选择。

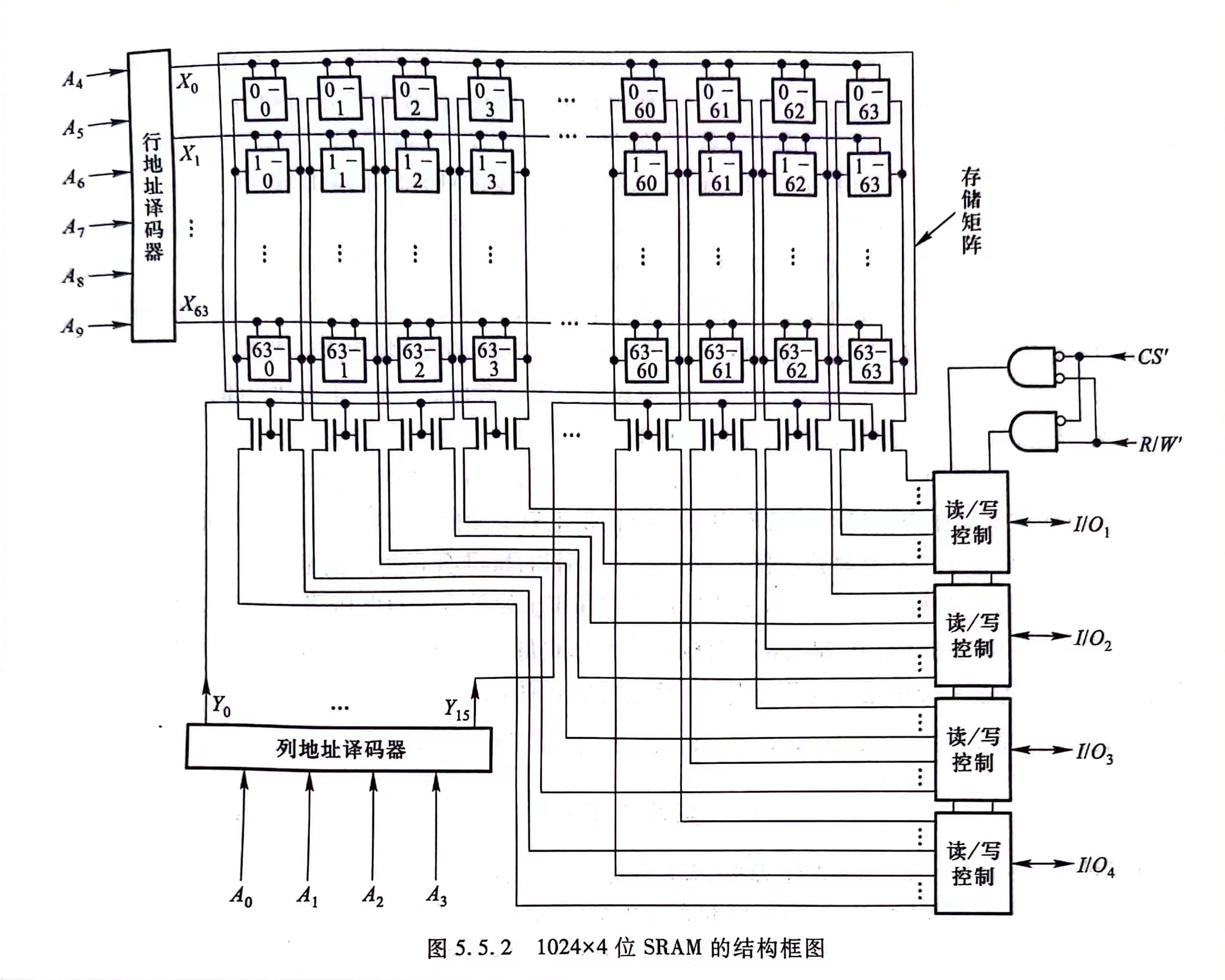

在下图中,行列地址译码器可以确定存储矩阵上哪个元素的 和 都导通,那么该元素才有可能被读取。

四、动态随机存储器(DRAM)

特点:大容量,高集成度,需要刷新。

五、只读存储器(ROM)

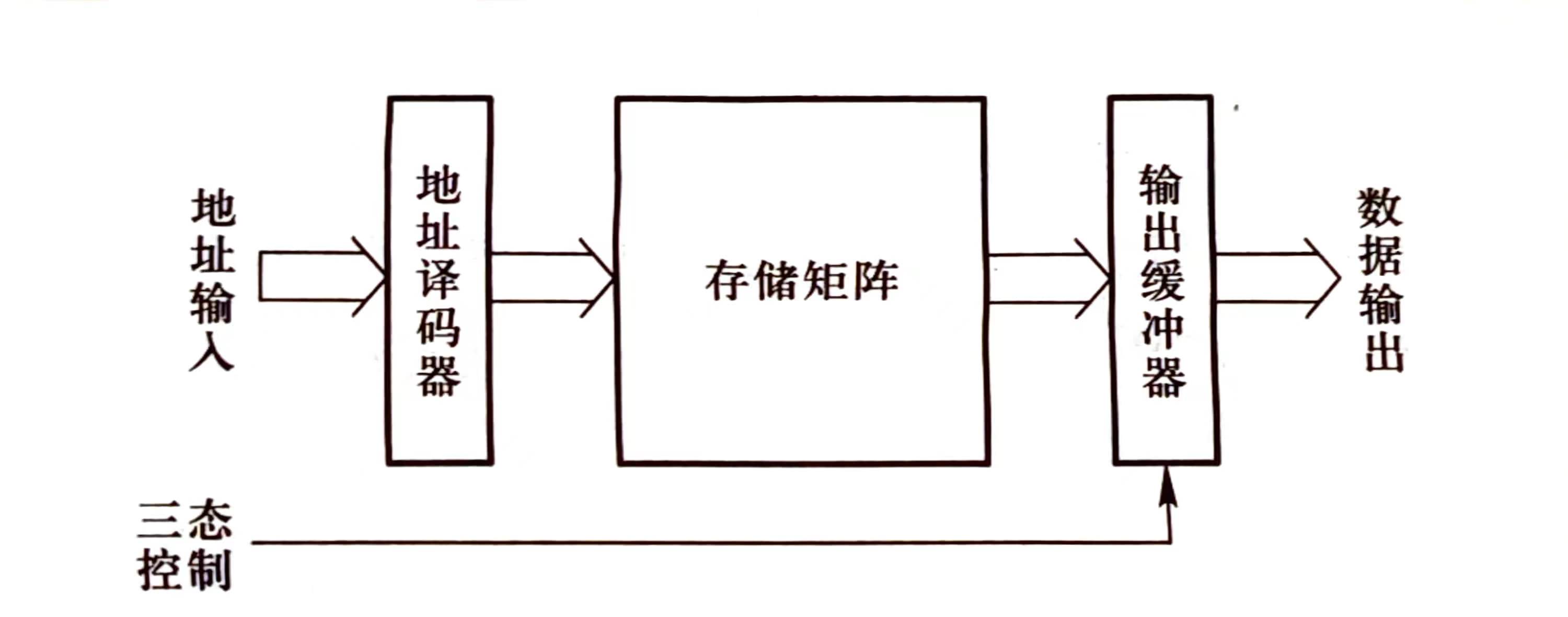

- 只读存储器的基本结构

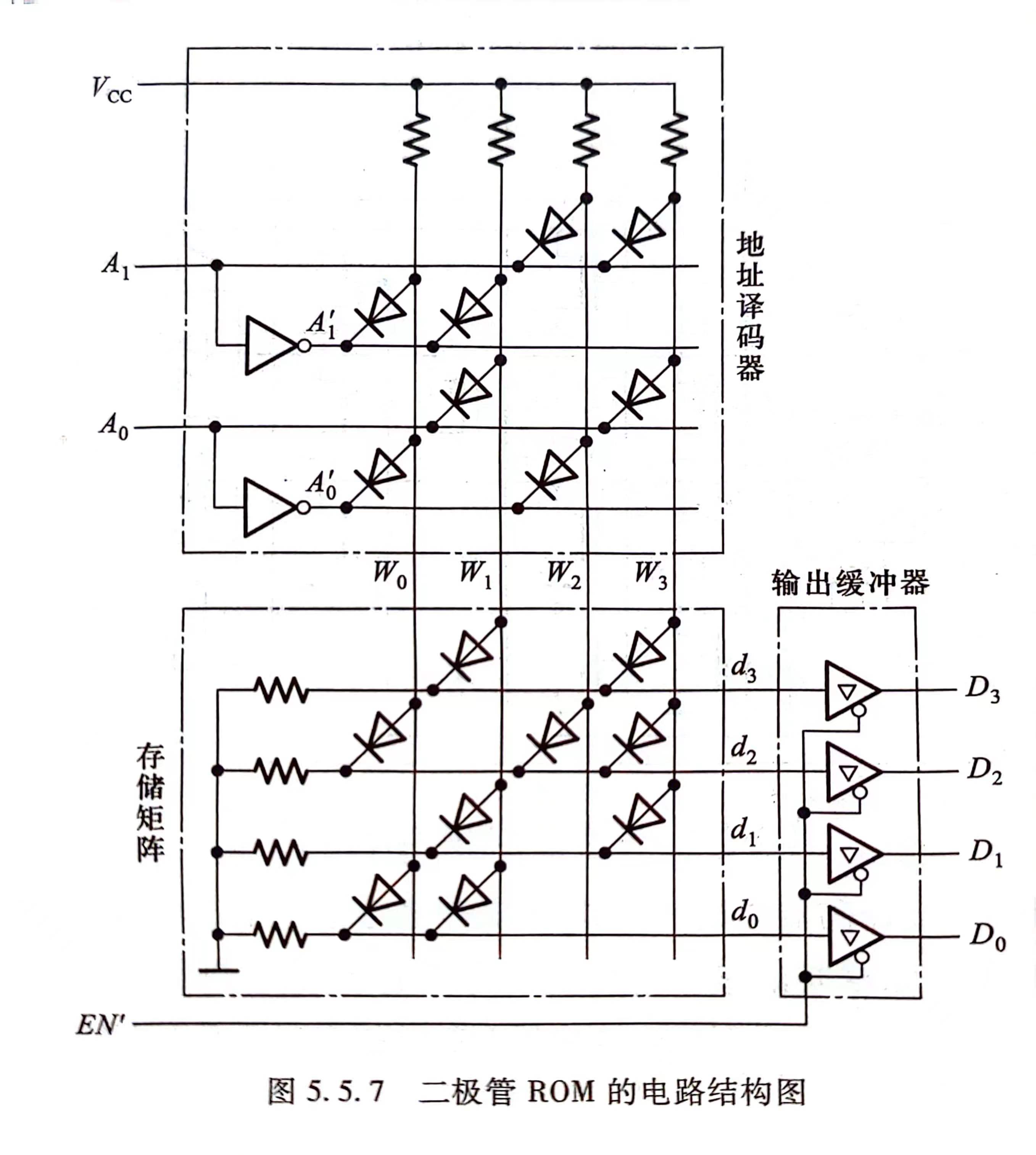

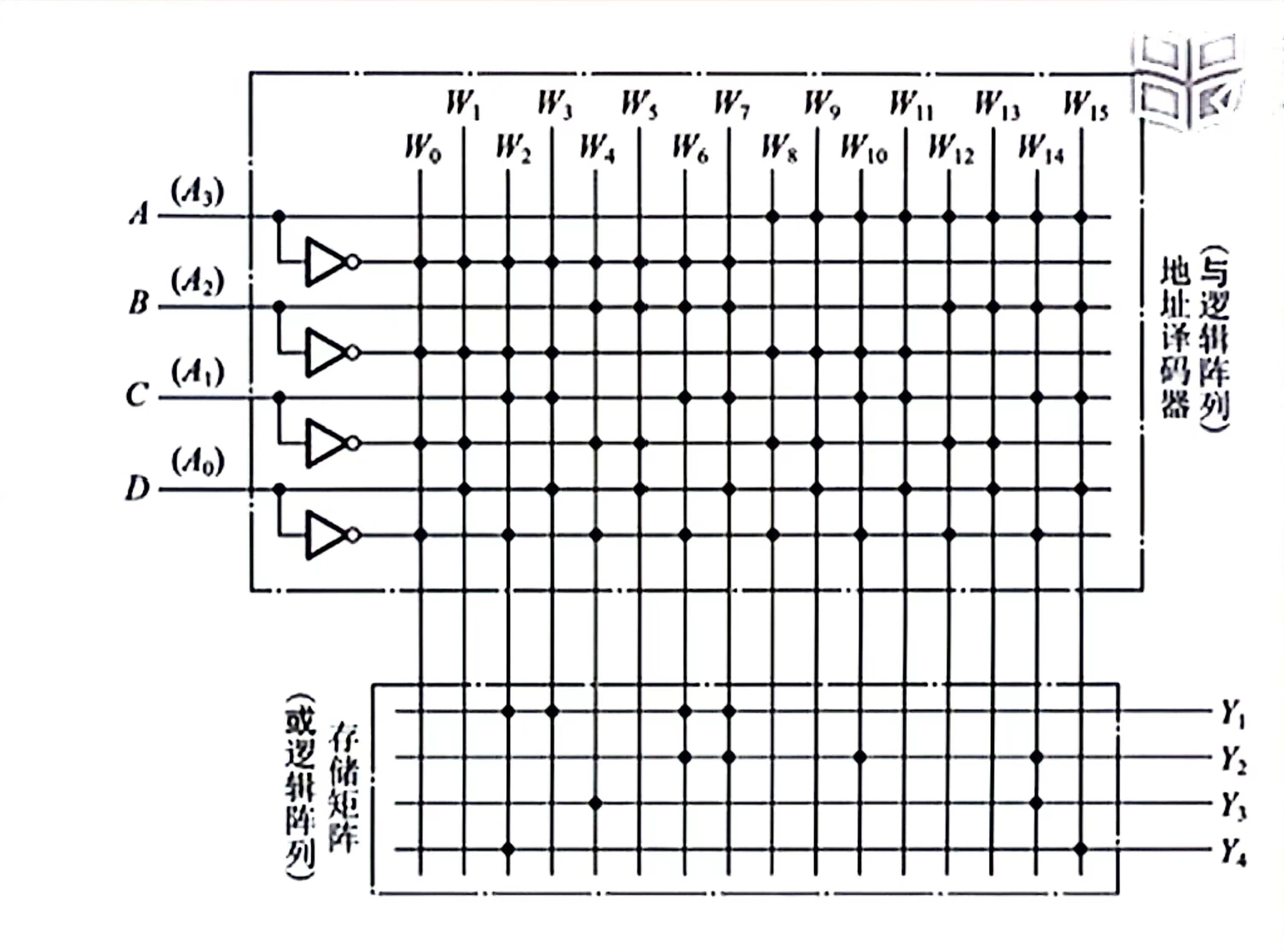

地址译码器由二极管与门构成,存储矩阵由或门构成。输出缓冲器则用于提高存储器的带负载能力,并实现对输出状态的三态控制。

其中$W_3$是字线,$d_0$是位线(数据线),而和则被称为地址线

与此同时,要通过给定的 信号决定对输出的三态控制。

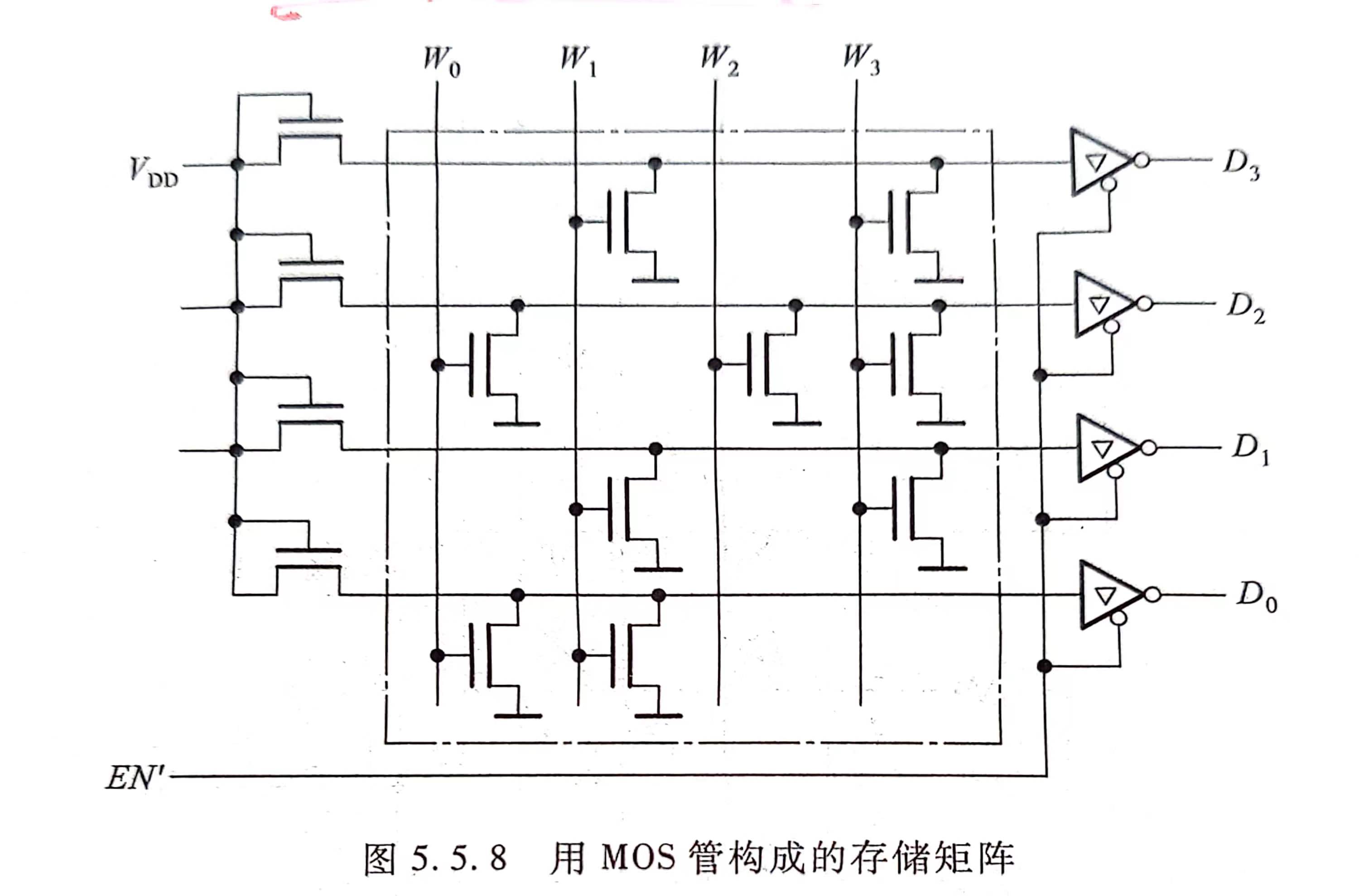

- 技巧:字线与位线的交叉点接有 MOS 管 / 二极管时相当于存1,没有接 MOS 管 / 二极管 时相当于存0

鉴于 MOS管中也有PN结,可以用来代替原来图中的PN结。对存储部分,可以有如下改造:

六、其他类型分ROM与闪存

- 掩模只读存储器(Mask ROM)

- 数据固化,不可以修改

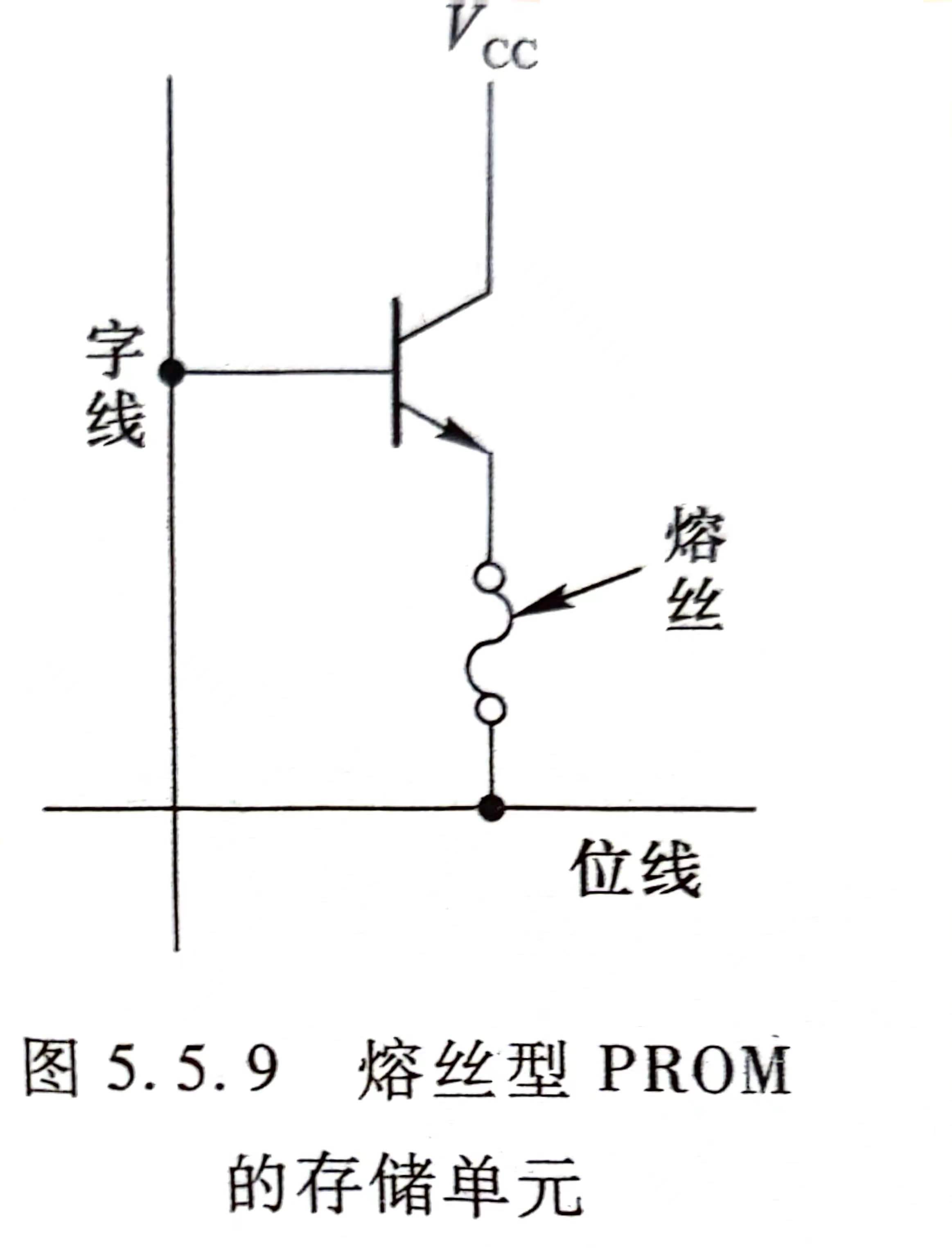

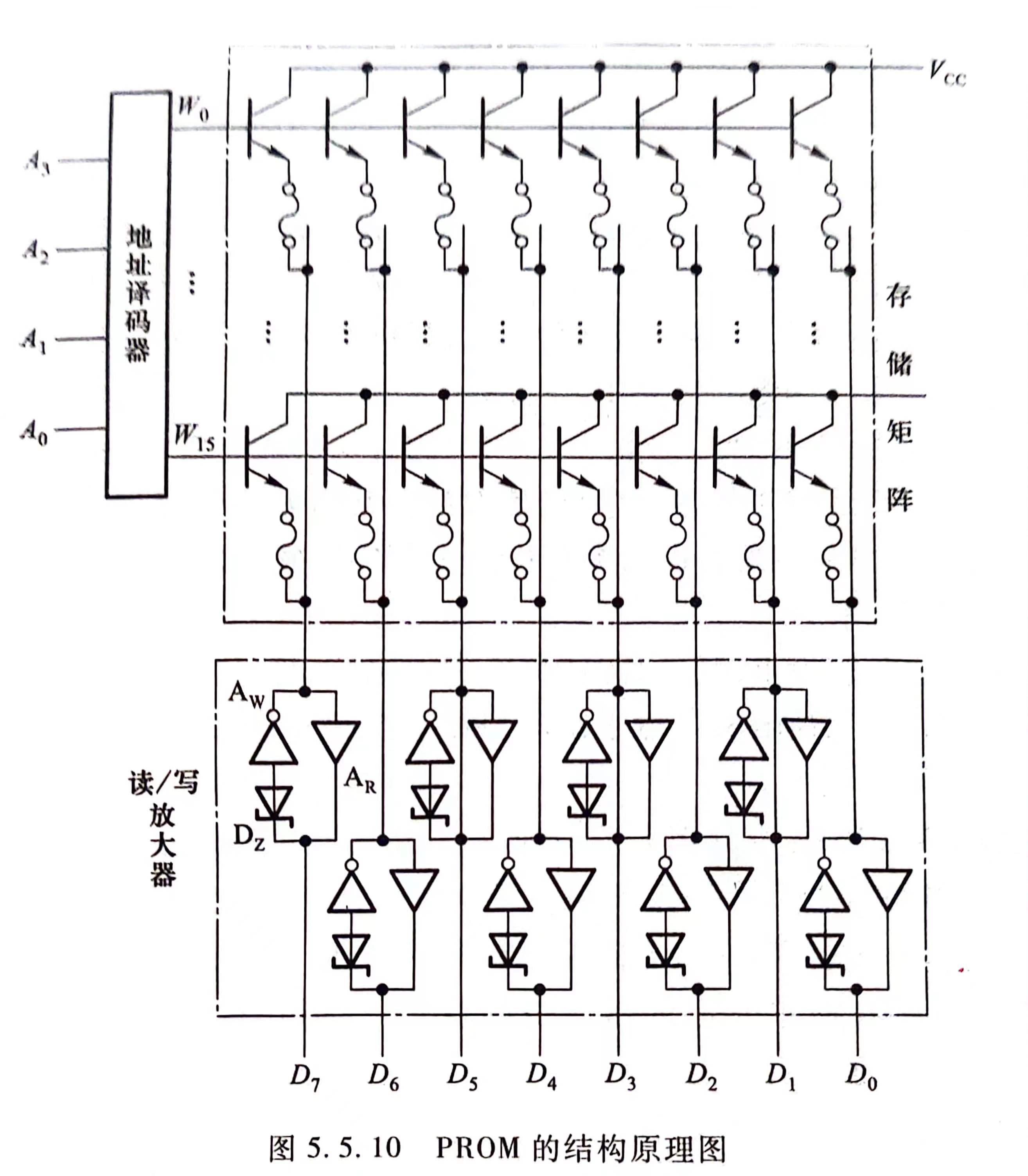

- 可编程只读存储器(PROM)

-

一次性:一经写入,不可修改

PROM结构示意图:

一开始存储阵列里面全是1,写入时在D_0~D_7

以下三种:、 以及闪存,都属于EPROM(可擦除可编程只读存储器)

- 紫外线擦除的只读存储器(UVEPROM)与电信号擦除的可编程只读存储器()

略

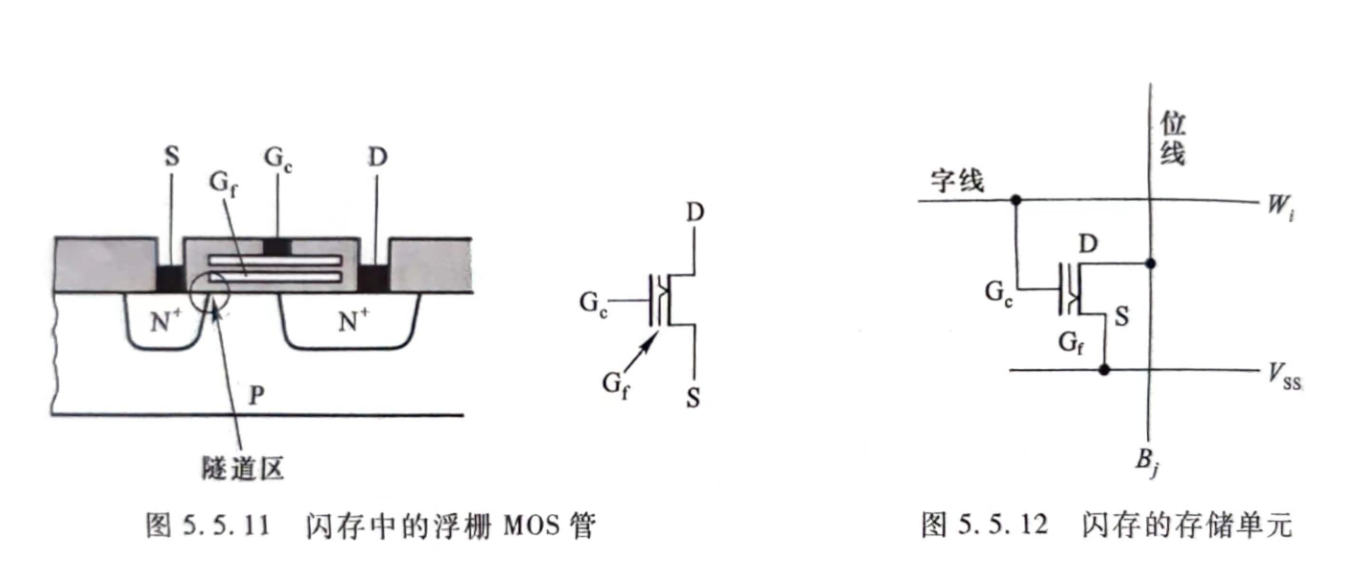

- 快闪存储器(闪存,Flash Memory)

闪存的存储单元是:一只浮栅MOS管除了控制栅 之外,在控制栅和衬底之间增加了一个浮置栅

工作原理:

-

在读出状态下

-

若浮置栅 上充有负电荷,

-

当字线给出高电平时浮栅MOS管截止,位线上输出高电平;

-

当字线给出低电平时浮栅MOS管导通,位线上输出低电平。

-

-

若浮置栅 $G_f $上没有负电荷,

-

当字线给出高电平时浮栅MOS管导通,位线上输出低电平;

-

当字线给出低电平时浮栅MOS管截止,位线上输出高电平。

-

-

-

在写入状态下

- 若浮置栅 的充电是利用雪崩注入的方法实现的:加正脉冲,加高电压,加0电平,直接雪崩击穿,高速电子到达浮置栅

-

在擦除状态下

- 置0,加正脉冲,产生导电隧道,之间电容小于之间电容,脉冲电压加到隧道,浮置栅上电子被导走。

特点:擦除快,写入慢

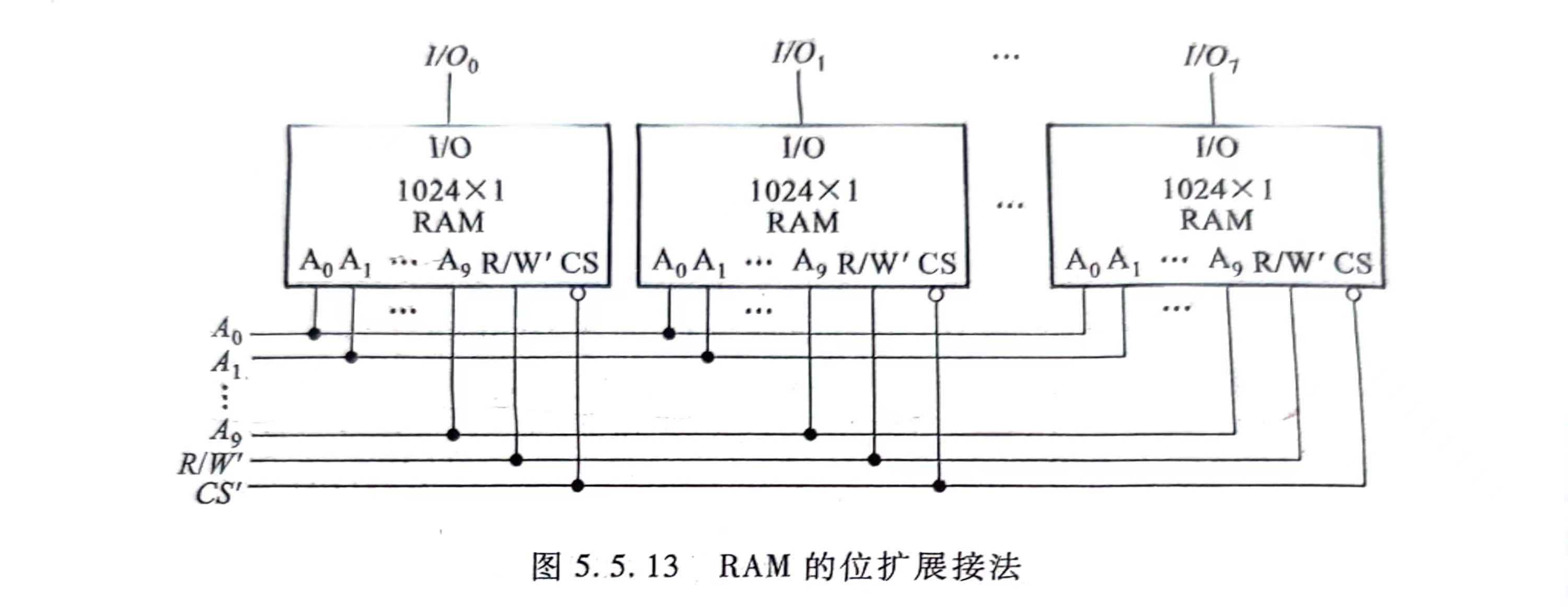

七、存储器容量的扩展

- 位扩展方式:直接联结

例如:用8片 的 RAM 接成一个 的RAM

对于ROM,除了上面没有 端之外,其余与RAM相同

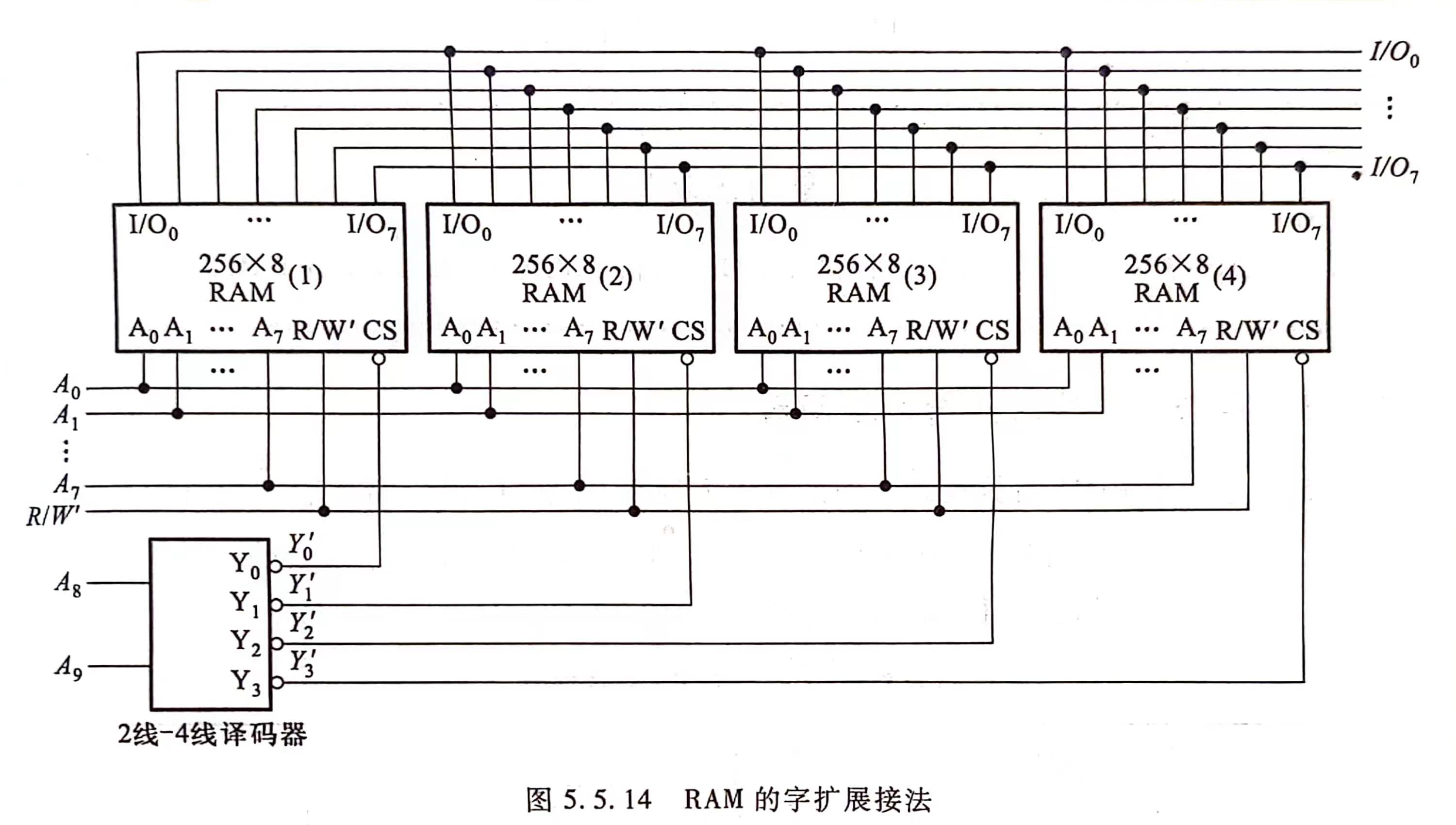

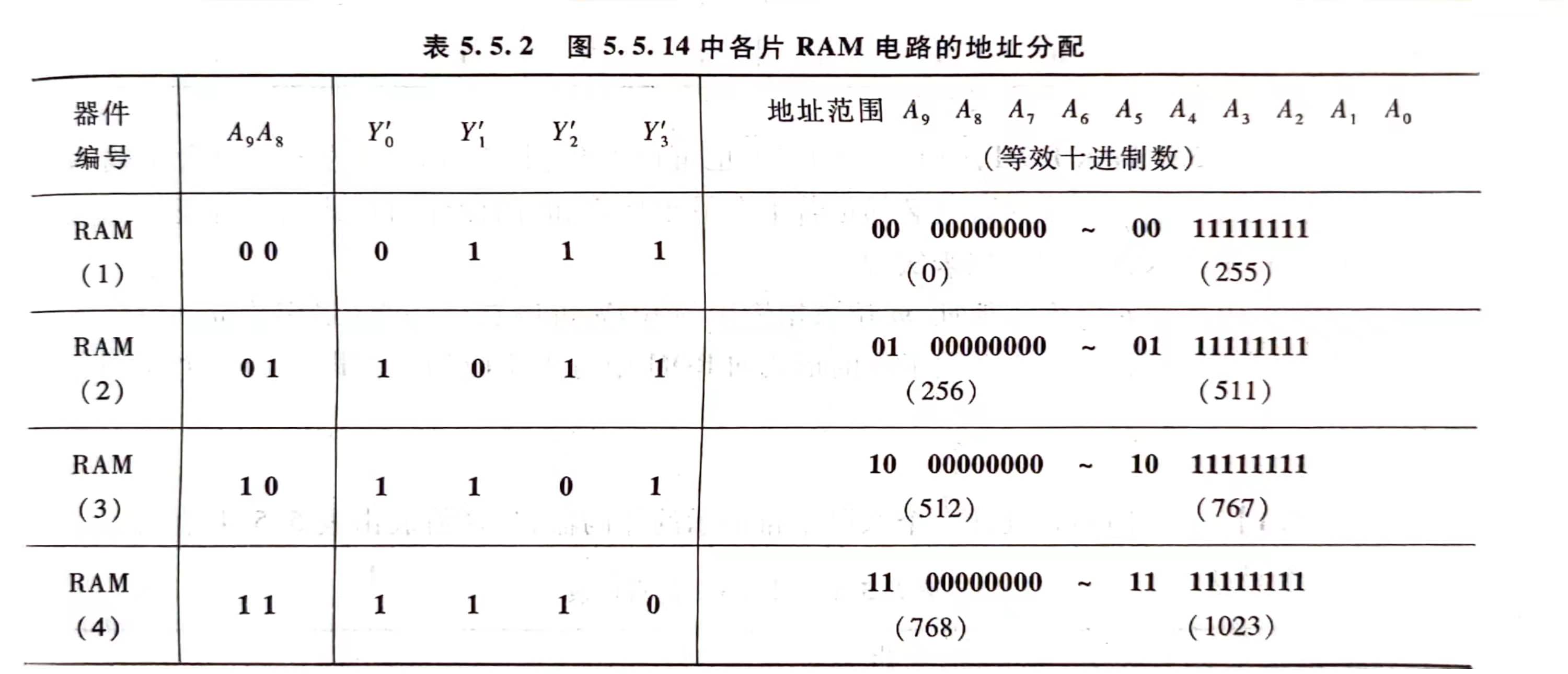

- 字扩展方式:使用译码器加地址端口数量

例如:用4片 的RAM接成一个 的RAM

增加两位地址代码和 译码器输出与各个RAM的CS端相连

则有:

上述接法也适用于ROM