加法器与减法器

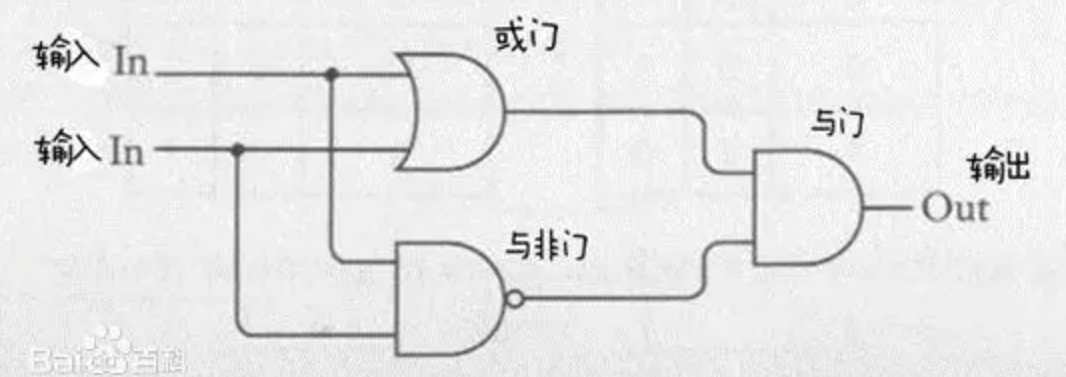

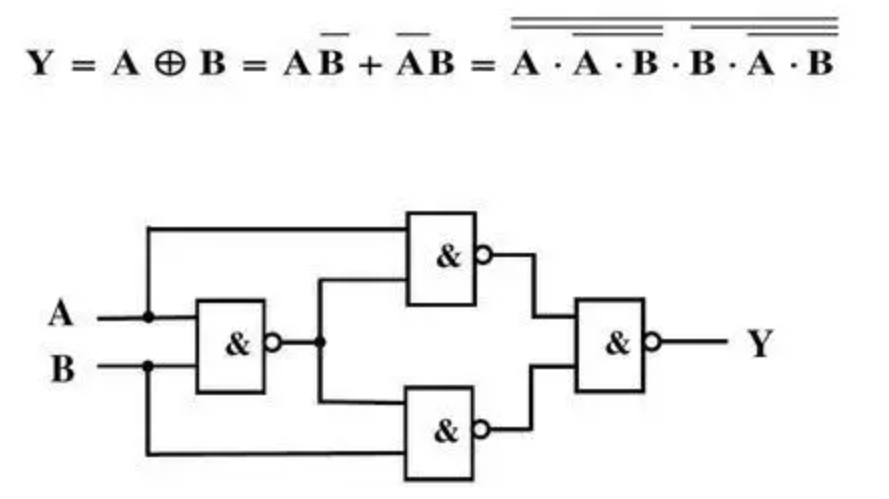

一、实现异或门的一种好方法:

使用最少继电器实现(只用了6个继电器)

使用单种逻辑门实现(用了8个继电器)

二、一位加法器

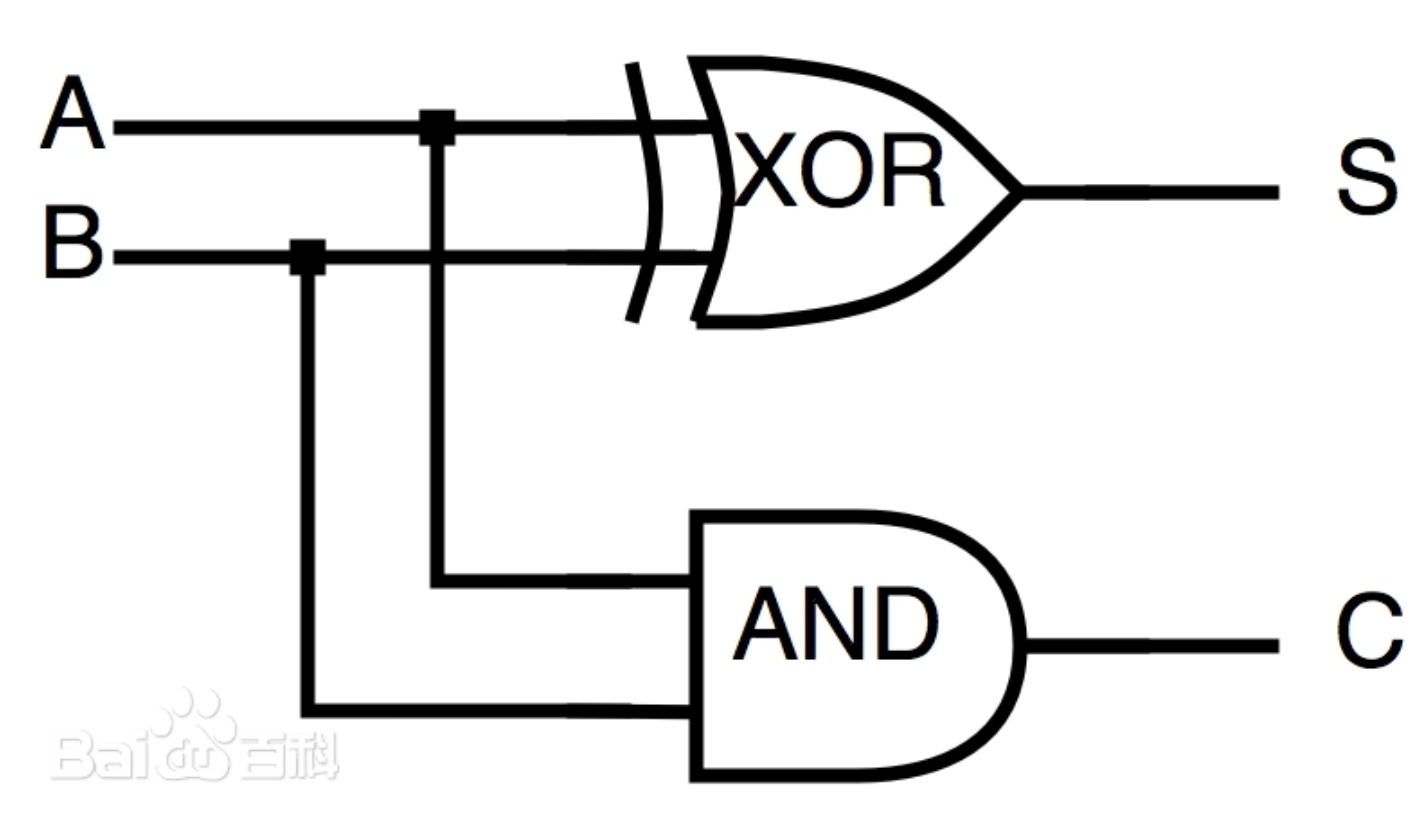

- 半加器

半加器(半加就是只求本位的和,暂不管低位送来的进位数)的逻辑状态表

| A | B | CO (进位信号) | S (本位和) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

逻辑表达式:

实现如下:(需要8个继电器)

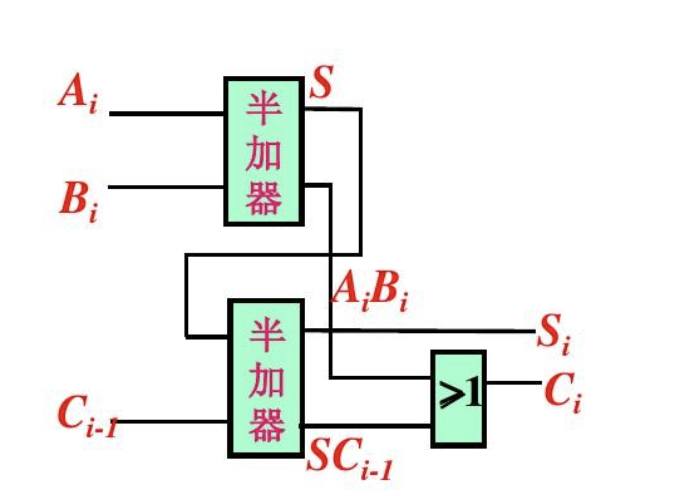

- 全加器(Full Adder)

将对应位的加数和来自低位进位的3个数相加

- 使用半加器实现全加器(需要18个继电器:)

值得注意的是,两个半加器的输出不可能全为1,所以将两个进位信号相或,即可得到输出。

二、多位加法器

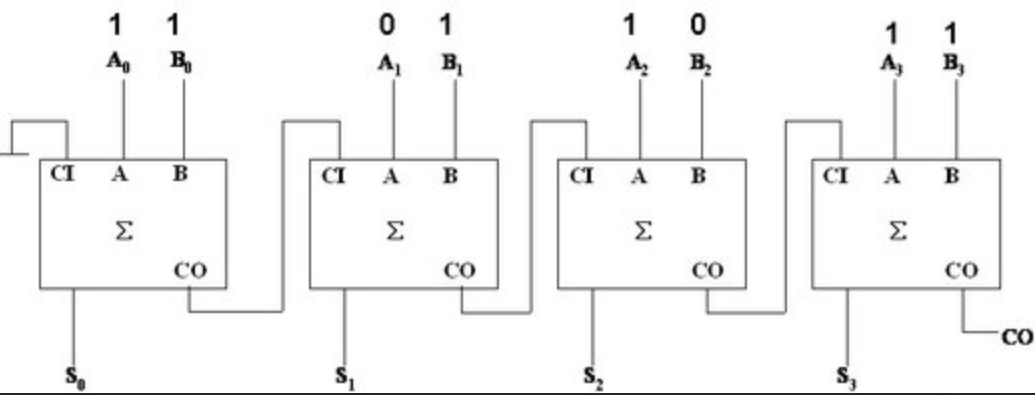

- 串行进行的多位加法器

缺点:运算速度慢(下图展示的是4位串行进位加法器)

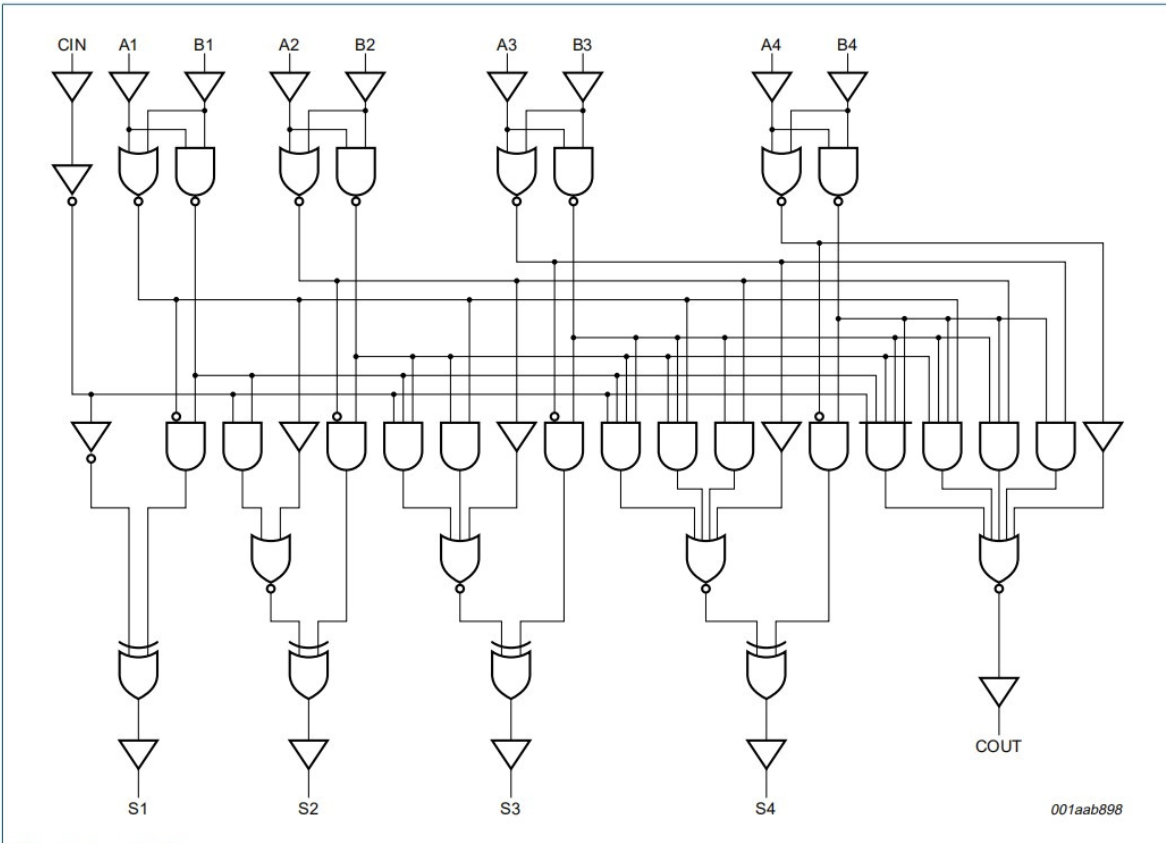

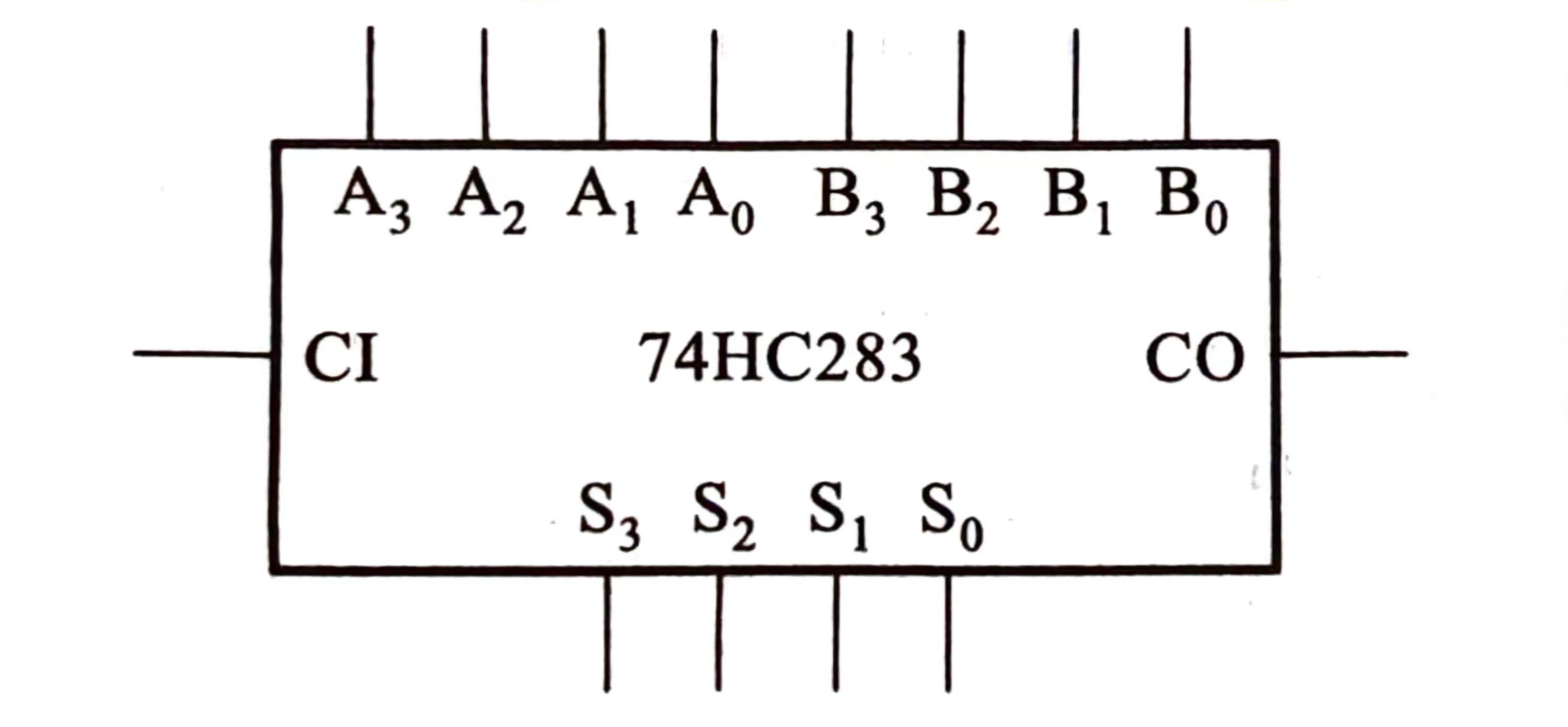

- 超前进位加法器(74HC283)

下图为一全加器真值表:

| CI | A | B | S | CO |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

先计算 :

可见:

定义:

-

进位生成函数

-

进位传送函数

则上述式子可以化简为

由于

迭代可得:

实际上在搭建过程中是将原始式子中所有的部分反向后完成,即有:

即:

而从全加器的真值表也可以得出 的逻辑表达式:

也就是:

三、减法器

1. 十进制数对9的补数(反码)与对10的补数(补码)

- 减法运算变为加法运算:求对9 的补数

如果计算:253-176

相当于计算:

253 + (999-176)+1-1000

- 循环排序的实现法:对所有数取10的补数

10的补数=9的补数+1

| -500 | -499 | … | -1 | 0 | 1 | … | 498 | 499 | 500 |

|---|---|---|---|---|---|---|---|---|---|

| 500 | 501 | … | 999 | 000 | 001 | … | 498 | 499 | 500 |

2. 二进制数对1的补数(二进制反码)和对2的补数(二进制补码)

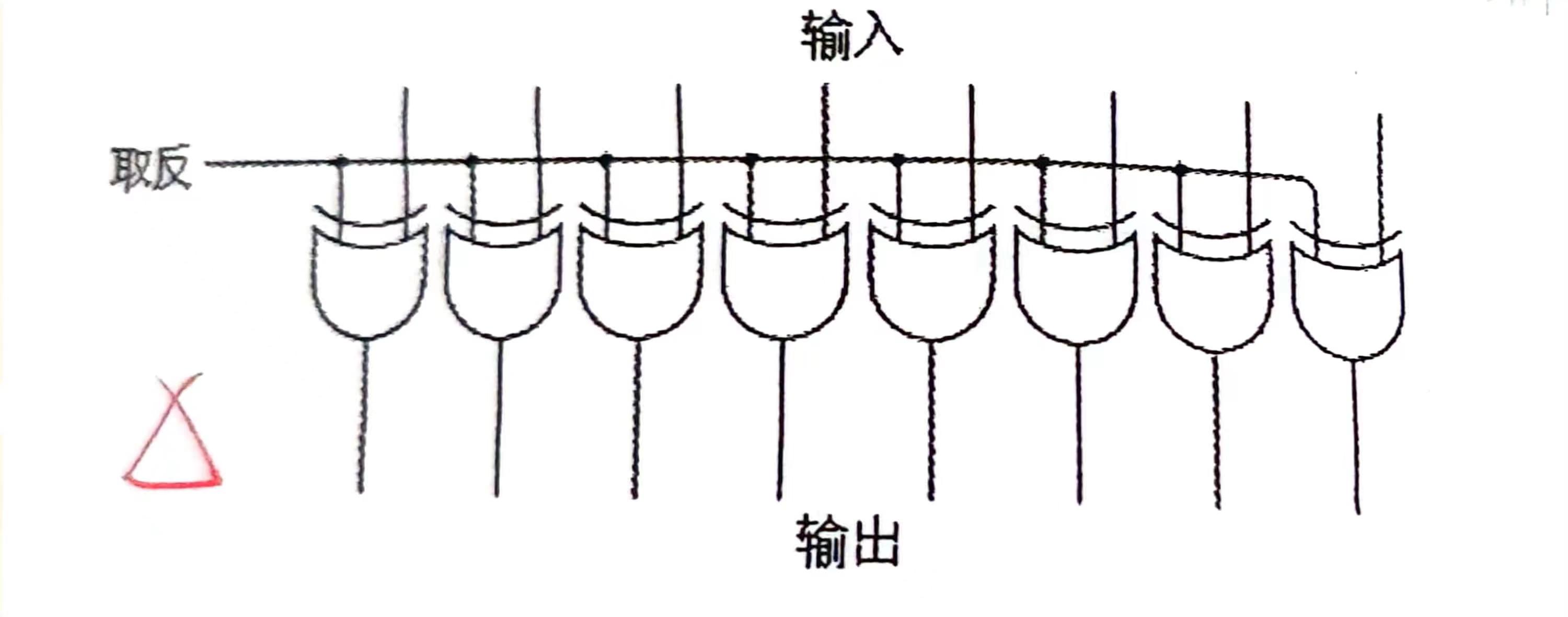

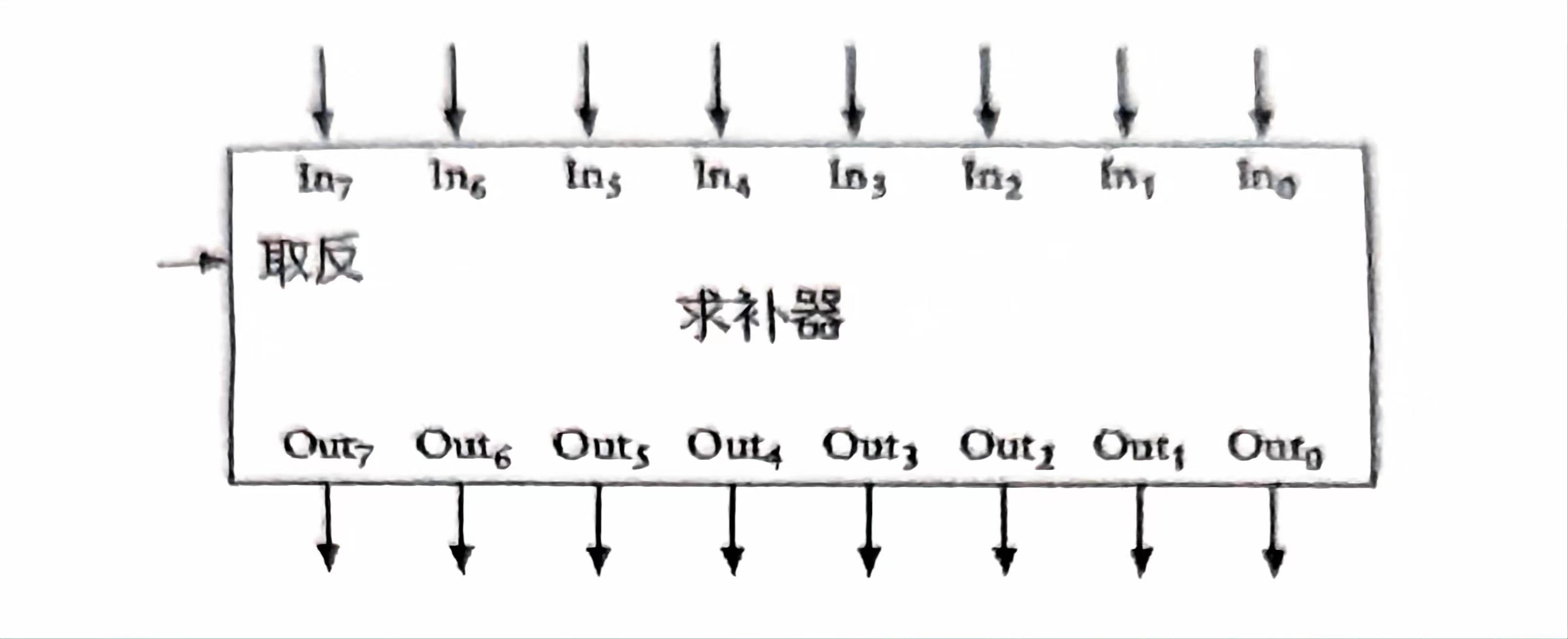

(1)异或门搭建的求补器

由于异或门的工作方式:

| XOR | 0 | 1 |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

当取反信号为0时,不取反,执行左边一列;当取反信号为1时, 取反,执行右边一列。

集成之后如下图:

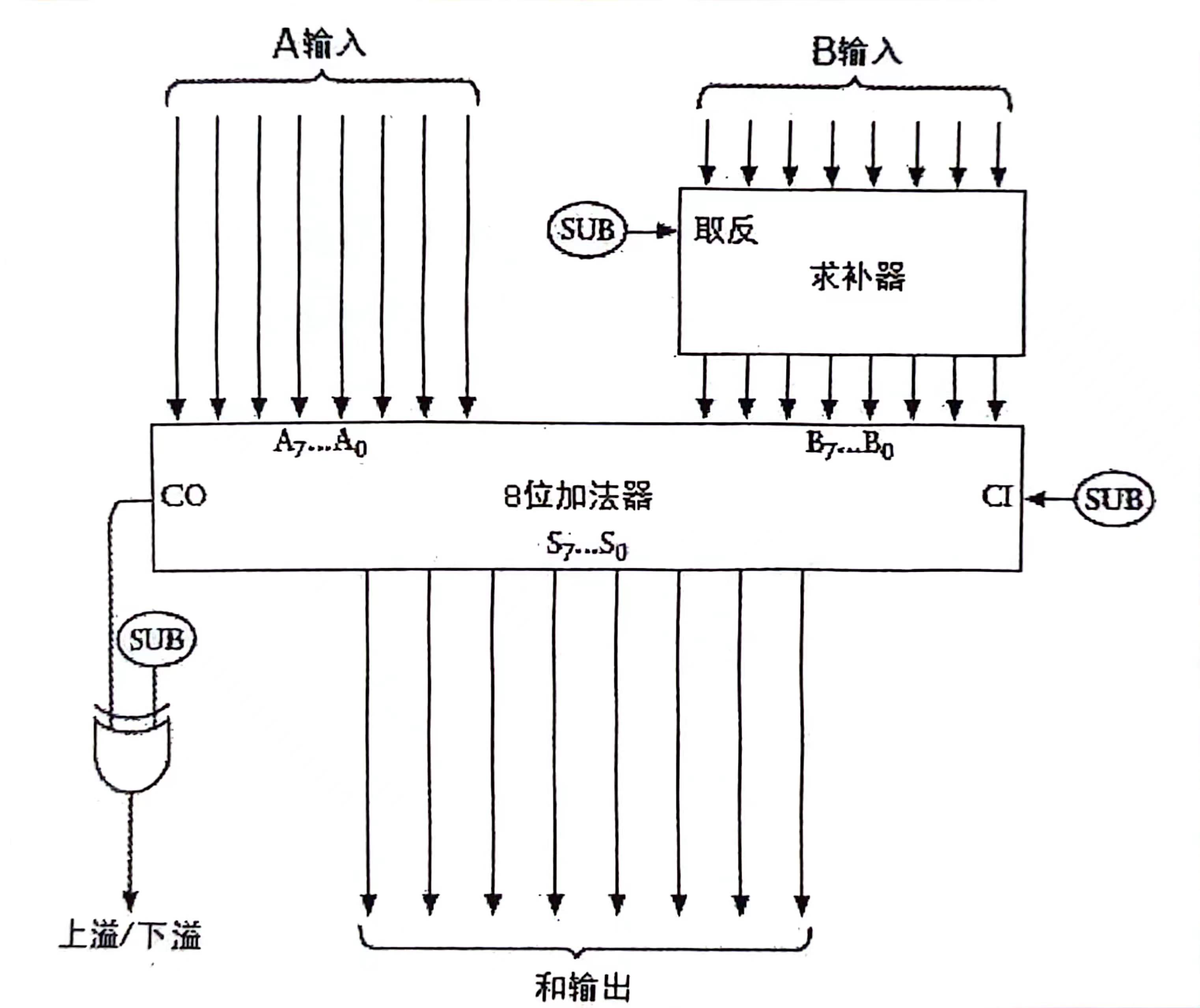

二进制减法器的实现如下:

当SUB信号输入0时,表相加。当SUB信号输入1时,表相减。

先看SUB=0的情况:

求补器不工作,输出与输入相同。即正常地把两个数相加。CI输入也是0。

而且输出的CO信号与SUB信号作异或运算,即当SUB=0,有输出信号Y=CO

若Y=1,则表示运算上溢(表示加法中得到的值大于八位二进制能表示的最大数字255)。

再看SUB=1的情况:

求补器工作,输出与输出反向。输入的$B_0$是取反之后的结果。这时`CI`的输入为1,加上后表示$B_7$取反结果+1

~表示的数为正数,补码为其本身。加法器相当于把两者的补码相加。

得到的和输出的是相减之后的结果(这怎么理解,见下)

比如253-176=77得到的是正数,没有下溢。

253 用二进制表示为1111 1101(也是它的补码)

176用二进制表示为1011 0000

-176的八位二进制补码为0101 0000

求和得到:1 0100 1101 (可见如果结果为正,是一定能溢出一位的,因为溢出是来源于我加上去的那个256,连0加上256 ,都能溢出一位。而假如结果没有溢出,只能说明结果本来就是负数)

这样算相当于253+(256-176)-256(-256的操作依靠取后8位实现)

又比方说176-253=-77,得到的是负数

176的二进制:1011 0000

-253的补码:0000 0011

求和后:1011 0011

(注意:这是179的二进制,求得-79的二进制需要在对这个数取反加一)

由上面这段文字可知,结果的CO位体现着结果的正负性。当CO为1的时候,表示输出的是正数;当CO为0的时候,表示输出的是负数。

当CO等于0的时候,我们只知道他是负的,不知道具体是多少,后续还要再对该数字做取反加一的后续操作,才能得到-77中的“77”这个信息。

-

当我们已经得到了176+(256-253)后:

后续的取反加一实际上是在做这个:256-(176+(256-253))

写在最后的注意事项:

无符号八位二进制数表示范围为:0~255

有符号八位二进制数表示范围为:-128~127